MCU锁相环简述(一)

来源:互联网 发布:最好的网络摄像头 编辑:程序博客网 时间:2024/04/19 15:52

在使用K60的过程中发现自己pllinit()不清楚,才发觉自己锁相环的概念还不懂,so,赶紧补补……

锁相环(PLL: Phase-locked loops)是一种利用反馈(Feedback)控制原理实现的频率及相位的同步技术,其作用是将电路输出的时钟与其外部的参考时钟保持同步。当参考时钟的频率或相位发生改变时,锁相环会检测到这种变化,并且通过其内部的反馈系统来调节输出频率,直到两者重新同步,这种同步又称为“锁相”(Phase-locked)。

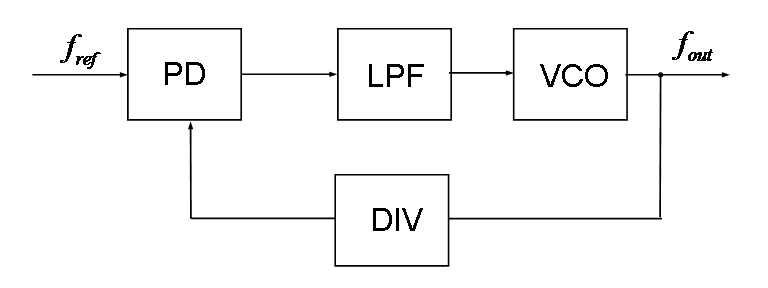

一个锁相环电路通常由以下模块构成:

- 鉴频鉴相器(PFD)(或鉴相器:PD)

- 低通滤波器(LPF)

- 压控振荡器(VCO)

- 反馈回路(通常由一个分频器(Frequency divider)来实现)

每个模块的简单原理描述如下:

- 鉴频鉴相器: 对输入的参考信号和反馈回路的信号进行频率和相位的比较,输出一个代表两者差异的信号至低通滤波器。

- 低通滤波器: 将输入信号中的高频成分滤除,保留直流部分送至压控振荡器。

- 压控振荡器: 输出一个周期信号,其频率由输入电压所控制。

- 反馈回路 : 将压控振荡器输出的信号送回至鉴频鉴相器。通常压控振荡器的输出信号的频率大于参考信号的频率,因此需在此加入分频器以降低频率。

以上呢,是在维基百科里的基本介绍,接下来说一下个人的一些理解:

在MCU中我们一般使用PLL进行倍频,用一个频率不高的晶振实现高频(貌似这句话不用讲^-^),这就是对锁相环倍频的应用。在百度百科里有这样一个介绍:

输入信号-> 鉴相器 -> 低通滤波器 -> 压控振荡器-> 输出信号。鉴相器有两个输入,分别是输入信号和压控振荡器的输出信号,在二者相位差和频率差不是很大的情况下,鉴相器的输出与两输入信号之差成正比,鉴相器的输出为模拟信号,其通过低通滤波器虑除高频杂波,后进入压控振荡器,压控振荡器的输出频率随其输入电压的改变而改变。从原理图上看,PLL实际上是一负反馈系统,只要输入信号在正常范围内,输出信号在“一定时间内”都能跟上。输入信号发生变化后,输出信号跟踪输入信号的过程称之为捕获;输出信号跟踪完毕时称之为锁定;输入信号变化过快导致输出信号无法跟踪时称为失锁。通过PLL可以方便实现N倍频,原理如下:

输入信号-> 鉴相器 -> 低通滤波器 -> 压控振荡器-> 输出信号

^|______N分频器______________|

此外,可以实现小数倍频,原理如下:

输入信号-> 鉴相器 -> 低通滤波器 -> 压控振荡器-> 输出信号

^|________N分频器/N+1分频_________|

| |

|------ 模式控制 ――---------> |

模式控制模块可以选择分频器处于N分频器还是N+1分频,若通过模式控制模块实现

10个clk中有9个clk为N分频,1个clk为N+1分频,则实际输出信号频率为(N+0.1)×

输入频率。

PLL电路本质是模拟电路,与ARM内核的数字电路截然不同,故在CPU中处于独立地

位,另外很多CPU的PLL供电为单独供电,且对PLL供电质量要求较高。

---------------------------------------------------------------------------------------------

上面已经对锁相环倍频的功能进行了说明,我们的MCU里就是集成了这样的电路,通过对外部的晶振进行倍频,从而达到我们需要的频率。下面就是对K60的锁相环实现进行理解了,下篇再写了……

0 0

- MCU锁相环简述(一)

- MCU低功耗设计(一)理论

- 异常简述(一)

- Windows可执行文件简述(一)

- Windows可执行文件简述(一)

- Windows可执行文件简述(一)

- Windows可执行文件简述(一)

- Windows可执行文件简述(一)

- C#多线程简述(一)

- Java集合简述(一)

- MCU破解技术分析(一)

- (转载)MCU浅谈

- MCU

- ActiveMQ(一):简述ActiveMQ及其机制

- Android Handler机制简述(一)

- 一、iOS简介(及简述操作系统)

- Android Sensor框架简述(一)

- Solr__luence(一)简述_入门

- 安卓学习笔记之SQLite数据库

- Tomcat 8(四)server.xml的Cluster标签详解

- JS正则表达式大全

- 数值计算方法程序库

- 创建主窗口

- MCU锁相环简述(一)

- oracle数据库中的锁

- 读《创造高收益的阿米巴模式》理解阿米巴的核心

- 判断单链表是否存在环,判断两个链表是否相交问题详解

- AWR报告分析(一)

- 解决Setting property 'source' to 'org.eclipse.jst.jee.server的问题

- The specified executable is not a validapplication for this OS platform.

- [ACM] hdu 2068 RPG的错排 (逆向思考,错排*组合累加)

- linux c线程池