【补充】关于ARM的PC指针异常返回处理(PC+8,PC+4,PC-4,PC-8情况)

来源:互联网 发布:linux密码修改 编辑:程序博客网 时间:2024/05/21 17:03

要理解PC指针,首先就要好好了解LR指针

连接寄存器LR(r14):用来保存和恢复PC寄存器的内容,它有两个特殊功能。

(1)保存子程序返回地址。使用BL或BLX时,跳转指令自动把返回地址放入r14中;子程序通过把r14复制到PC来实现返回,通常用下列指令之一:

MOV PC, LR

BX LR

通常子程序这样写,保证了子程序中还可以调用子程序。

stmfd sp!, {lr}

……

ldmfd sp!, {pc}

(2)当异常发生时,异常模式的r14用来保存异常返回地址,将r14如栈可以处理嵌套中断。

程序计数器r15(PC):PC是有读写限制的。当没有超过读取限制的时候,读取的值是指令的地址加上8个字节,由于ARM指令总是以字对齐的,故bit[1:0]总是00。当用str或stm存储PC的时候,偏移量有可能是8或12等其它值。在V3及以下版本中,写入bit[1:0]的值将被忽略,而在V4及以上版本写入r15的bit[1:0]必须为00,否则后果不可预测。

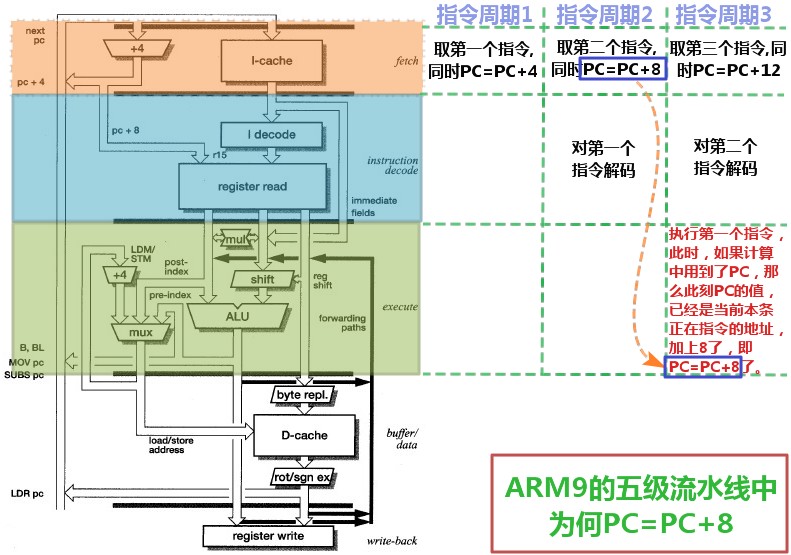

知道PC寄存器和LR寄存器功能以后,再了解一下ARM处理器的三级流水线和多级流水线

首先,对于ARM7对应的流水线的执行情况,如下面这个图所示:

从图中可以看出,一条汇编指令的运行有三个步骤,取指、译码、执行,当第一条汇编指令取指完成后,紧接着就是第二条指令的取指,然后第三条...如此嵌套

其实很容易看出,第一条指令:

add r0, r1,#5

取指完成后,PC就指向了第二条指令,此时PC=PC+4

当第一条指令译码完成以后,此时PC=PC+8

所以第一条指令开始执行时,PC值已经加了8

所以必须记住这个前提,在arm中,每次该指令执行时,其实这时的PC值是PC=PC+8

由于此处不是本文重点,更多关于多级流水线和PC为什么是PC+8的详细内容,点此跳转。

接下来谈谈我们在arm汇编时,什么时候需要PC-4, PC-8, PC什么都不减

!记住:PC不是指向你正在运行的指令,而是PC始终指向你要取的指令的地址

我们以下面uboot中的start.S的最开始的汇编代码为例来进行解释:

00000000 <_start>: 0:ea000014 b58 <reset> 4:e59ff014 ldrpc, [pc, #20]; 20 <_undefined_instruction> 8:e59ff014 ldrpc, [pc, #20]; 24 <_software_interrupt> c:e59ff014 ldrpc, [pc, #20]; 28 <_prefetch_abort> 10:e59ff014 ldrpc, [pc, #20]; 2c <_data_abort> 14:e59ff014 ldrpc, [pc, #20]; 30 <_not_used> 18:e59ff014 ldrpc, [pc, #20]; 34 <_irq> 1c:e59ff014 ldrpc, [pc, #20]; 38 <_fiq>00000020 <_undefined_instruction>: 20:00000120 .word0x00000120

流水线如表格:指令物理地址Cycle1Cycle2Cycle3Cycle4Cycle5Cycle60 4取指译码执行 8 取指译码执行 c 取指译码执行 10 取指译码执行14 取指译码18 取指红色加粗字体代表:实际PC的物理地址(即PC始终指向你要取的指令的地址)

- 指令周期Cycle1

- 取指

PC总是指向将要读取的指令的地址(即我们常说的,指向下一条指令的地址),而当前PC=4,

所以去取物理地址为4对对应的指令

ldrpc, [pc, #20]

其对应二进制代码为e59ff014。

此处取指完之后,自动更新PC的值,即PC=PC+4(单个指令占4字节,所以加4)=4+4=8

- 取指

- 指令周期Cycle2

- 译指

翻译地址为4的指令e59ff014

- 同时再去取指

PC总是指向将要读取的指令的地址(即我们常说的,指向下一条指令的地址),而当前PC=8,

所以去物理地址为8所对应的指令“ldr pc, [pc, #20]” 其对应二进制代码为e59ff014。

此处取指完之后,自动更新PC的值,即PC=PC+4=8+4=12=0xc

- 译指

- 指令周期Cycle3

- 执行(指令)

执行“e59ff014”,即

ldrpc, [pc, #20]

所对表达的含义,即PC

= PC + 20

= 12 + 20

= 32

= 0x20

此处,只是计算出待会要赋值给PC的值是0x20,这个0x20还只是放在执行单元中内部的缓冲中。

- 译指

翻译地址为8的指令e59ff014

- 取指

此步骤由于是和上面a.中的执行同步做的,所以,未受到影响,继续取指,而取指的那一时刻,PC为上一Cycle更新后的值,即PC=0xc,所以是去取物理地址为0xc所对应的指令

ldrpc, [pc, #20]

对应二进制为e59ff014 此处取指完之后,自动更新PC的值,即PC=PC+4=0xc+4=0x10

- 执行(指令)

用图来总结过程:

再记住:改变PC的值,会导致流水线清空!!!

好了,那我们继续来看什么时候需要PC-4, PC-8, PC什么都不减

这个取决于是在正常程序的跳转还是发生异常:

我先假设当前运行上面地址4所对应的指令,将它称作第一条指令!<即现在状态为上面cycle3>

正常跳转:

如果是使用BL执行了正常程序的跳转,那么执行这条BL指令时,由于是正常的跳转指令,所以cpu会将下一句的物理地址存放在LR中,那么将8地址存放在LR中),当从子程序跳转回来的时候,那么就需要将保存在LR寄存器中的值恢复给PC寄存器,mov PC, LR 这样的指令返回

异常跳转:

由于我们当前执行的是地址4对应的第一条指令,无论什么异常我们恢复都应该回到地址8对应的第二条指令。(回来的时候,会清空流水线重新开始按照逻辑计算。)

IRQ异常发生时,因为这个异常是在指令执行时候发生的,即cpu还没有自动更新pc值,所以将地址4+8=c保存在LR中。但是LR寄存器中保存的是4+8=c,指向的第三条指令,如果不进行减4处理,我们回来将会漏执行第二条指令,所以PC恢复的时候就需要LR减4,所以正常从子程序返回的时候会使用如:

SUBS PC, LR,#4 返回到当前指令的下一条指令

未定义指令异常时,因为这个异常发生在指令译码时,即cpu还没有自动更新pc值,所以将地址4+4=8保存到LR中;因为该指令未定义,所以返回时就不应该返回到这条未定义指令,而是返回到它的下一条指令,R14中保存的刚好就是下一条指令的地址,所以就不用计算了,直接将R14赋值给PC就行了,即mov PC, LR

预取指令异常是在流水线的执行时才进入异常,即cpu还没有自动更新pc值,所以将地址4+8=c保存到LR中;所以返回时应该返回到下一条指令,所以PC恢复的时候就需要R14减4,即SUBS PC, LR,#4

数据中止异常,这个异常表示当前存储器的访问不能完成,是在本指令执行完成后才发生的,即cpu已经自动更新pc值,所以将地址4+8+4=0x14保存到LR中,所以从异常返回时,需要从第一条指令的下一条指令(第二条指令)开始执行,所以PC恢复的时候就需要R14减8,即SUBS PC, LR,#8

【参考资料】:

crifan的文章

双刃剑客的博客

- 【补充】关于ARM的PC指针异常返回处理(PC+8,PC+4,PC-4,PC-8情况)

- 关于ARM的PC指针(什么时候PC+8,PC+4,PC-4,PC-8)

- 关于ARM的PC指针(什么时候PC+8,PC+4,PC-4,PC-8)

- ARM获得PC指针为何PC=PC+8

- 【转】ARM获得PC指针为何PC=PC+8[上](转)

- 【转】ARM获得PC指针为何PC=PC+8[下](转)

- 【转】ARM获得PC指针为何PC=PC+8[下](转)

- 【转】ARM获得PC指针为何PC=PC+8[下](转)

- pc

- 为啥PC = PC + 8 ARM

- PC+4得到PC+12的原因

- 关于 PC指针问题

- uart(3)pc->arm->pc

- arm异常中lr保存pc的情况

- PC指针的问题

- ARM9流水线PC=PC+8

- 为何ARM7中PC=PC+8

- ARM中断返回SUB pc lr-irq #4

- LeetCode-17:Letter Combinations of a Phone Number

- jQuery 遍历查找到的每一个结果

- 使用input读取文件

- 各种正则验证

- 深入理解Python中的进程

- 【补充】关于ARM的PC指针异常返回处理(PC+8,PC+4,PC-4,PC-8情况)

- poj-3734

- 将博客搬至CSDN

- 判断单链表是否带环? 若带环, 求环的长度? 求环的入口点?

- MapReduce 中文版论文

- LeetCode-18:4Sum

- Codeforces Round #417 (Div. 2) 题解

- 游戏开发中的人工智能(二):追逐和闪躲

- Linux 查看文件内容的基础命令操作