ADI时钟抖动衰减器优化JESD204B串行接口功能

来源:互联网 发布:mac 最火游戏排行 编辑:程序博客网 时间:2024/06/03 09:17

Analog Devices, Inc.,全球领先的高性能信号处理解决方案供应商,最近推出一款高性能时钟抖动衰减器HMC7044,其支持JESD204B串行接口标准,适用于连接基站设计中的高速数据转换器和现场可编程门阵列(FPGA)。JESD204B接口专门针对高数据速率系统设计需求而开发,3.2 GHz HMC7044时钟抖动衰减器内置可以支持和增强该接口标准特性的独特功能。HMC7044提供50 fs抖动性能,可改善高速数据转换器的信噪比和动态范围。该器件提供14路低噪声且可配置的输出,可以灵活地与许多不同的器件接口。HMC7044还具有各种时钟管理和分配特性,使得基站设计人员利用单个器件就能构建完整的时钟设计。

本文引用地址:http://www.eepw.com.cn/article/279911.htm

查看产品页面、下载数据手册、申请样片和订购评估板:http://www.analog.com/pr150909/hmc7044

通过在线技术支持社区EngineerZone®联系工程师和ADI产品专家: https://ezchina.analog.com/community/rf

更多有关产品信息,请致电亚洲技术支持中心:400 6100 006, 或发送邮件至 china.support@analog.com , 也可点击ADI官方微博http://weibo.com/analogdevices ,或通过手机登录m. analog.com 或 www.analog.com了解最新产品等信息。

更多ADI产品及应用视频,请访问:http://videos.analog.com/category/chinese/

基站应用中有许多串行JESD204B数据转换器通道需要将其数据帧与FPGA对齐。HMC7044时钟抖动衰减器可在数据转换器系统中产生源同步且可调的样本和帧对齐(SYSREF)时钟,使JESD204B系统设计得以简化。该器件具有两个锁相环(PLL)和重叠的片内压控振荡器(VCO)。第一PLL将一个低噪声、本地压控时钟振荡器(VCXO)锁定至噪声相对较高的参考,而第二PLL将VCXO信号倍频至VCO频率,仅增加非常小的噪声。对于蜂窝基础设施JESD204B时钟产生、无线基础设施、数据转换器时钟、微波基带卡和其它高速通信应用,HMC7044架构可提供出色的频率产生性能,相位噪声和积分抖动均很低。

HMC7044时钟抖动衰减器主要特性

支持JEDEC JESD204B

超低均方根抖动:50 fs(12 KHz至20 MHz,典型值)

噪底:-162 dBc/Hz (245.76 MHz)

低相位噪声:<-142 dBc/Hz(800 kHz至983.04 MHz输出频率)

PLL2提供多达14路差分器件时钟

支持最高5 GHz的外部VCO输入

片内稳压器提供出色的PSRR

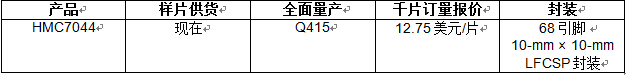

报价与供货

锁相环相关文章:锁相环原理

- ADI时钟抖动衰减器优化JESD204B串行接口功能

- 详解JESD204B串行接口时钟需求及其实现方法

- JESD204B接口与协议

- 具有报警功能的串行实时时钟

- 串行接口

- 串行接口

- 串行接口

- 串行接口

- 串行接口

- 时钟 扇出 缓冲器 Ti adi

- ADI

- WEB ADI 注册功能的SQL 语句

- 并/串行接口

- 串行通信接口

- 常用串行接口总结

- 21 串行接口封装

- 串行异步通信接口

- 串行接口芯片16550

- 什么是for语句

- (005) java后台开发之Mac终端命令运行java

- Oracle常用操作

- 如何提高 Java 中锁的性能

- 初识sklearn,了解clustering

- ADI时钟抖动衰减器优化JESD204B串行接口功能

- python tornado下的csrf怎么玩?

- xLua添加白名单

- 关于2017的面试准备与记录

- Android studio中获取sha1 和MD5 值

- Deep Learning读书笔记8--应用

- centOS7安装Nginx

- vue简单下拉框组件

- 机器学习入门笔记(九)----无监督学习