吹尽黄沙始见金,历述CPU架构与工艺

来源:互联网 发布:windows防火墙功能 编辑:程序博客网 时间:2024/05/16 19:56

吹尽黄沙始见金,历述CPU架构与工艺

http://www.sina.com.cn 2006年04月18日 19:28 走进中关村

【编者按】这篇文章的作者叫濮元恺,是兰州一个正在上高二的学生。他利用寒假的时间写出了这篇稿件,确实让人惊讶和钦佩。姑且不论他的观点是否正确,单是组织这么多内容对于一个高中生来说,就属相当不易。我们企盼着小濮在未来的日子中,继续关注IT业,关注计算机产品,关注走进中关村网站。

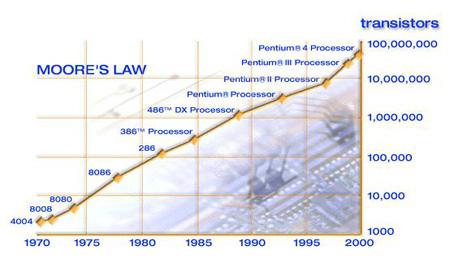

四十多年前,Intel的创始人戈登摩尔(Gordon Moore)通过长期的对比,研究后发现:CPU中的部件(我们现在所说的晶体管)在不断增加,其价格也在不断下降。“随着单位成本的降低以及单个集成电路集成的晶体管数量的增加;到1975年,从经济学来分析,单个集成电路应该集成65000个晶体管。”Intel此后几年的发展都被摩尔提前算在了纸上,使人们大为惊奇,“摩尔定律”也名声大振。为了让人们更直观地了解摩尔定律,摩尔及其同事总结出一句极为精练的公式 “集成电路所包含的晶体管每18个月就会翻一番”。

从摩尔定律之诞生后,芯片产业有了前进的方向:为了不断提升性能,工程师要做的是不断向芯片中添加足够多的晶体管。但这个方向很快就受到了挑战,Intel在70年代末就发现摩尔定律的预测偏离了实际,并做出了少许修改。其实摩尔定律起初只是简单观察的结果,不过却由Intel不断扩充和执行下以及成为他们最喜欢的方式,同时也是这家技术水平高、生产潜力大的企业的最有利可图的模式。

在2003年ISSCC大会上,摩尔本人就指出了摩尔定律中的另一个错误,即晶圆尺寸的发展并没有按照摩尔定律预测在2003年发展到53英寸,现在只发展到12英寸(300mm)。2003年摩尔本人提出对摩尔定律质疑的主要原因,就是半导体生产工艺在0.18mm后漏电率快速上升,到0.13mm后更为严重。漏电率快速上升现象的出现,使得90nm、65nm及以后的半导体生产工艺、尤其是需要高速运行的CPU生产工艺面临严峻挑战。

摩尔定律在拉动着芯片产业飞奔的同时,在现实中的表现也常常让人们担心。国际半导体技术蓝图机构(ITRS)为IC组件的发展起草了一份雄心勃勃的发展规划,同时也提出警告,晶体管数目的增长速度显著快于设计能力的提高速度。不过,ITRS认为在设计技术之外,设计成本才是对半导体技术可持续发展的最大威胁,并导致设计和生产力之间产生鸿沟。在CPU生产厂商方面,按照摩尔定律这个速度发展,到本世纪末,处理器生产线投资至少是数千亿乃至上万亿美元。谁投资得起?投资能回收吗?IT产业能在这个方向上健康发展下去吗?

但另外一个现象引起又我们注意:摩尔认为,尽管摩尔定律并不总是正确的,却似乎总可以延续下去。按照专业人士的分析,CPU的发展在触及摩尔定律的极限之前,将朝着更高性能、更低功耗、更低成本的方向发展,在可预见的未来,CPU的处理能力将继续保持高速增长,小型化、集成化永远是发展趋势。

总之在过去的四十多年,半导体工业的发展突破了一个又一个看似不可能跨越的瓶颈,神奇地遵循着摩尔定律,如今的半导体科技已经达到了几乎不可能为之的地步。而这一切都得益于生产技术的不断进步,可以预见伴随着处理器的发展,生产技术这种发展趋势仍将持续下去。

从实际情况来看,Intel最新发布的桌面级CPU——Pentium Extreme Edition 955,使用更先进的65 nm制程,集成了3亿7600万个晶体管。已走入不惑之年的摩尔定律面临不少问题,比如计算机整体架构落伍、漏电率和功耗、经济鸿沟,但其还继续着辉煌,这是为什么呢。下文将从生产工艺和芯片设计的角度阐述当今CPU的发展趋势,希望能解答大家对当今CPU发展的少许不解,以便让大家火眼金睛看清这场精彩纷呈的CPU斗争。

1、CPU的生产过程

要了解CPU的生产工艺,我们需要先知道CPU是怎么被制造出来的。让我们分几个步骤学习CPU的生产过程。

(1) 硅提纯

生产CPU等芯片的材料是半导体,现阶段主要的材料是硅Si,这是一种非金属元素,从化学的角度来看,由于它处于元素周期表中金属元素区与非金属元素区的交界处,所以具有半导体的性质,适合于制造各种微小的晶体管,是目前最适宜于制造现代大规模集成电路的材料之一。

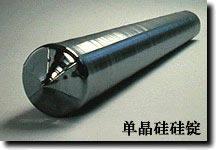

在硅提纯的过程中,原材料硅将被熔化,并放进一个巨大的石英熔炉。这时向熔炉里放入一颗晶种,以便硅晶体围着这颗晶种生长,直到形成一个几近完美的单晶硅。以往的硅锭的直径大都是200毫米,而CPU厂商正在增加300毫米晶圆的生产。

(2)切割晶圆

硅锭造出来了,并被整型成一个完美的圆柱体,接下来将被切割成片状,称为晶圆。晶圆才被真正用于CPU的制造。所谓的“切割晶圆”也就是用机器从单晶硅棒上切割下一片事先确定规格的硅晶片,并将其划分成多个细小的区域,每个区域都将成为一个CPU的内核(Die)。一般来说,晶圆切得越薄,相同量的硅材料能够制造的CPU成品就越多。

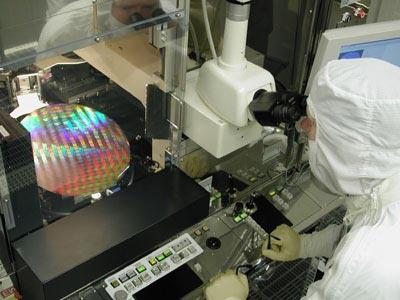

(3)影印(Photolithography)

在经过热处理得到的硅氧化物层上面涂敷一种光阻(Photoresist)物质,紫外线通过印制着CPU复杂电路结构图样的模板照射硅基片,被紫外线照射的地方光阻物质溶解。而为了避免让不需要被曝光的区域也受到光的干扰,必须制作遮罩来遮蔽这些区域。这是个相当复杂的过程,每一个遮罩的复杂程度得用10GB数据来描述。

(4)蚀刻(Etching)

这是CPU生产过程中重要操作,也是CPU工业中的重头技术。蚀刻技术把对光的应用推向了极限。蚀刻使用的是波长很短的紫外光并配合很大的镜头。短波长的光将透过这些石英遮罩的孔照在光敏抗蚀膜上,使之曝光。接下来停止光照并移除遮罩,使用特定的化学溶液清洗掉被曝光的光敏抗蚀膜,以及在下面紧贴着抗蚀膜的一层硅。

然后,曝光的硅将被原子轰击,使得暴露的硅基片局部掺杂,从而改变这些区域的导电状态,以制造出N井或P井,结合上面制造的基片,CPU的门电路就完成了。

(5)重复、分层

为加工新的一层电路,再次生长硅氧化物,然后沉积一层多晶硅,涂敷光阻物质,重复影印、蚀刻过程,得到含多晶硅和硅氧化物的沟槽结构。重复多遍,形成一个3D的结构,这才是最终的CPU的核心。每几层中间都要填上金属作为导体。Intel的Pentium 4处理器有7层,而AMD的Athlon 64则达到了9层。层数决定于设计时CPU的布局,以及通过的电流大小。

(6)封装

这时的CPU是一块块晶圆,它还不能直接被用户使用,必须将它封入一个陶瓷的或塑料的封壳中,这样它就可以很容易地装在一块电路板上了。封装结构各有不同,但越高级的CPU封装也越复杂,新的封装往往能带来芯片电气性能和稳定性的提升,并能间接地为主频的提升提供坚实可靠的基础。

(7)多次测试

测试是一个CPU制造的重要环节,也是一块CPU出厂前必要的考验。这一步将测试晶圆的电气性能,以检查是否出了什么差错,以及这些差错出现在哪个步骤(如果可能的话)。接下来,晶圆上的每个CPU核心都将被分开测试。

由于SRAM(静态随机存储器,CPU中缓存的基本组成)结构复杂、密度高,所以缓存是CPU中容易出问题的部分,对缓存的测试也是CPU测试中的重要部分。

每块CPU将被进行完全测试,以检验其全部功能。某些CPU能够在较高的频率下运行,所以被标上了较高的频率;而有些CPU因为种种原因运行频率较低,所以被标上了较低的频率。最后,个别CPU可能存在某些功能上的缺陷,如果问题出在缓存上,制造商仍然可以屏蔽掉它的部分缓存,这意味着这块CPU依然能够出售,只是它可能是Celeron等低端产品。

当CPU被放进包装盒之前,一般还要进行最后一次测试,以确保之前的工作准确无误。根据前面确定的最高运行频率和缓存的不同,它们被放进不同的包装,销往世界各地。

2、不断进步的生产工艺

随着生产工艺的进步,CPU应该是越做越小?可为什么现在CPU好像尺寸并没有减少多少,那么是什么原因呢?实际上CPU厂商很希望把CPU的集成度进一步提高,同样也需要把CPU做得更小,但是因为现在的生产工艺还达不到这个要求。

生产工艺这4个字到底包含些什么内容呢,这其中有多少高精尖技术的汇聚,CPU生产厂商是如何应对的呢?下文将根据上面CPU制造的7个步骤展开叙述,让我们一起了解当今不断进步的CPU生产工艺。

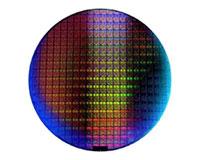

(1)晶圆尺寸

硅晶圆尺寸是在半导体生产过程中硅晶圆使用的直径值。硅晶圆尺寸越大越好,因为这样每块晶圆能生产更多的芯片。比如,同样使用0.13微米的制程在200mm的晶圆上可以生产大约179个处理器核心,而使用300mm的晶圆可以制造大约427个处理器核心,300mm直径的晶圆的面积是200mm直径晶圆的2.25倍,出产的处理器个数却是后者的2.385倍,并且300mm晶圆实际的成本并不会比200mm晶圆来得高多少,因此这种成倍的生产率提高显然是所有芯片生产商所喜欢的。

然而,硅晶圆具有的一个特性却限制了生产商随意增加硅晶圆的尺寸,那就是在晶圆生产过程中,离晶圆中心越远就越容易出现坏点。因此从硅晶圆中心向外扩展,坏点数呈上升趋势,这样我们就无法随心所欲地增大晶圆尺寸。

总的来说,一套特定的硅晶圆生产设备所能生产的硅晶圆尺寸是固定的,如果对原设备进行改造来生产新尺寸的硅晶圆的话,花费的资金是相当惊人的,这些费用几乎可以建造一个新的生产工厂。不过半导体生产商们也总是尽最大努力控制晶圆上坏点的数量,生产更大尺寸的晶圆,比如8086 CPU制造时最初所使用的晶圆尺寸是50mm,生产Pentium 4时使用200mm的硅晶圆,而Intel新一代Pentium 4 Prescott则使用300mm尺寸硅晶圆生产。300mm晶圆被主要使用在90纳米以及65纳米的芯片制造上。

(2)蚀刻尺寸

蚀刻尺寸是制造设备在一个硅晶圆上所能蚀刻的一个最小尺寸,是CPU核心制造的关键技术参数。在制造工艺相同时,晶体管越多处理器内核尺寸就越大,一块硅晶圆所能生产的芯片的数量就越少,每颗CPU的成本就要随之提高。反之,如果更先进的制造工艺,意味着所能蚀刻的尺寸越小,一块晶圆所能生产的芯片就越多,成本也就随之降低。比如8086的蚀刻尺寸为3μm,Pentium的蚀刻尺寸是0.80μm,而Pentium 4的蚀刻尺寸当前是0.09μm(90纳米)。目前Intel的300mm尺寸硅晶圆厂可以做到0.065μm(65纳米)的蚀刻尺寸。

此外,每一款CPU在研发完毕时其内核架构就已经固定了,后期并不能对核心逻辑再作过大的修改。因此,随着频率的提升,它所产生的热量也随之提高,而更先进的蚀刻技术另一个重要优点就是可以减小晶体管间电阻,让CPU所需的电压降低,从而使驱动它们所需要的功率也大幅度减小。所以我们看到每一款新CPU核心,其电压较前一代产品都有相应降低,又由于很多因素的抵消,这种下降趋势并不明显。

我们前面提到了蚀刻这个过程是由光完成的,所以用于蚀刻的光的波长就是该技术提升的关键。目前在CPU制造中主要是采用2489埃和1930埃(1埃=0.1纳米)波长的氪/氟紫外线,1930埃的波长用在芯片的关键点上,主要应用于0.18微米和0.13微米制程中,而目前Intel是最新的90纳米制程则采用了波长更短的1930埃的氩/氟紫外线。

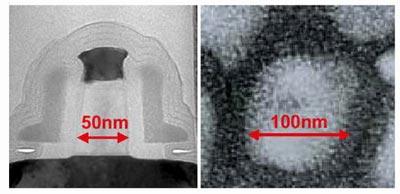

90纳米的晶体管大小(左)与流行感冒病毒的大小(右)比较:

以上两点就是CPU制造工艺中的两个因素决定,也是基础的生产工艺。这里有些问题要说明一下。Intel是全球制造技术最先进且拥有工厂最多的公司(Intel有10家以上的工厂做CPU),它掌握的技术也相当多,后面有详细叙述。AMD和Intel相比则是一家小公司,加上新工厂Fab36,它有3家左右的CPU制造工厂。同时AMD没有能力自己研发很多新技术,它主要是通过战略合作关系获取技术。

在0.25微米制程上,AMD和Intel在技术上处于同一水平,不过在向0.18微米转移时落在了后面。在感觉无法独自赶上Intel之后,AMD和摩托罗拉建立了战略合作伙伴关系。摩托罗拉拥有很多先进的电子制造技术,用于Apple电脑PowerPC的芯片HiPerMOS7(HiP7)就是他们完成的;AMD在获得授权后一下子就拥有了很多新技术,其中部分技术甚至比Intel的0.13微米技术还要好。现在AMD选择了IBM来共同开发65纳米和45纳米制造技术。它选择的这些都是相当有前景的合作伙伴,特别是IBM,一直作为业界的技术领袖,它是第一个使用铜互连、第一个使用低K值介电物质、第一个使用SOI等技术的公司。AMD获得的大多数技术很先进,而且对生产设备的要求不高,生产成本控制的很低,这也是AMD的优势。

图为AMD的新工厂Fab36中采用的APM 3.0 (Automated Precision Manufacturing)技术,可进一步实现制造的自动化,效率化。同时AMD还建造了自己的无尘实验室。

(3)金属互连层

在前面的第5节“重复、分层”中,我们知道了不同CPU的内部互连层数是不同的。这和厂商的设计是有关的,但它也可以间接说明CPU制造工艺的水平。这种设计没有什么好说的了,Intel在这方面已经落后了,当他们在0.13微米制程上使用6层技术时,其他厂商已经使用7层技术了;而当Intel准备好使用7层时,IBM已经开始了8层技术;当Intel在Prescott中引人7层带有Low k绝缘层的铜连接时,AMD已经用上9层技术了。更多的互连层可以在生产上亿个晶体管的CPU(比如Prescott)时提供更高的灵活性。

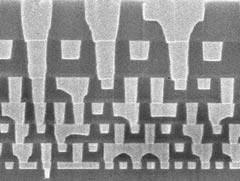

7层金属铜互连技术显微图片:

我们知道当晶体管的尺寸不断减小而处理器上集成的晶体管又越来越多的时候,连接这些晶体管的金属线路就更加重要了。特别是金属线路的容量直接影响信息传送的速度。在90纳米制程上,Intel推出了新的绝缘含碳的二氧化硅来取代氟化硅酸盐玻璃,并同时表示这可以增加18%的内部互连效率。

3、CPU制造工艺前进方向

在现有常规工艺的支撑下,CPU很难再向前发展,并且遇到越来越多的障碍,接下来讨论CPU的继续发展方向。

目前存在着两种泄漏电流:首先是门泄漏,这是电子的一种自发运动,由负极的硅底板通过管道流向正极的门;其次是通过晶体管通道的硅底板进行的电子自发从负极流向正极的运动。这个被称作亚阈泄漏或是关状态泄漏(也就是说当晶体管处于“关”的状态下,也会进行一些工作)。这两者都需要提高门电压以及驱动电流来进行补偿。这种情况自然的能量消耗以及发热量都有负面的影响。

现在让我们回顾一下场效应晶体管中的一个部分——在门和通道之间的绝缘二氧化硅(silicon dioxide)薄层。这个薄层的作用就相当于一个电子屏障,用途也就是防止门泄漏。很显然,这个层越是厚,其阻止泄漏的效果就越好。不过还要考虑它在通道中的影响,如果我们想要缩短通道(也就是减小晶体管体积),就必须减少这个层。在过去的10年中,这个薄层的厚度已经逐渐达到整个通道长度的1/45。目前,处理器厂商们正在做的是使这个层越来越薄,而不顾随之增加的门泄漏。不过这个方式也有它的限度,Intel的技术员说这个薄层的最小厚度是2.3纳米,如果低于这个厚度,门泄漏将急剧增大。这也是摩尔本人提到的“漏电率快速上升”而制约摩尔定律继续前进。

到目前为止,处理器厂商还没有对亚阈泄漏做什么工作,不过这一情况很快就要改变了。操作电流和门操作时间是标志晶体管性能的两个主要参数,而亚阈泄漏对两者有不小的影响。为了保证晶体管的性能,厂商们不得不提高驱动电流来得到想要的结果。这点在主板的供电系统和电源规范中有明显体现,我们也可以理解为什么越来越多的供电和散热规范是Intel等CPU厂商提出的。

(1)SOI技术

在所有的解决方案中,SOI(Silicon on Insulator,绝缘层上覆硅)看上去最有前景。关键很其实现很简单:晶体管通过一个更厚的绝缘层从硅晶元中分离出来。

这样做具有很多优点:首先,这样在晶体管通道中就不会再有不受控制的电子运动,也就不会对晶体管电子特性有什么影响;其次,在将阈值电压加载到门电路上后,驱动电流出现前通道电离的时间间隔也减小了,也就是说,晶体管“开”和“关”状态的切换性能提高了,这可是晶体管性能的第二大关键性能参数;同时在速度不变的情况下,我们可以也可以降低阈值电压,或是同时提高性能和降低电压。

举个例子来说,如果阈值电压保持不变,性能可以提高30%,那么如果我们将频率保持不变而将注意力集中在节能性上,那么我们也可以节省大约50%的能耗。此外,在晶体管本身可以处理各种错误时(比如空间例子进入通道进行电离),通道的特性也变得容易预计了。而SOI不足在于必须减小晶体管漏极/源区域的深度,而这将导致晶体管阻抗的升高。同时,SOI技术也意味着晶体管的成本提高了10%。

(2)Low K互连层技术

关于功耗和漏电问题,还有一个大家耳熟能详的技术就是Low K互连层。

在集成电路工艺中,有着极好热稳定性、抗湿性的二氧化硅一直是金属互联线路间使用的主要绝缘材料。随着互联中导线的电阻(R)和电容(C)所产生的寄生效应越来越明显,低介电常数材料替代传统绝缘材料二氧化硅也就成为集成电路工艺发展的又一必然选择。

这里的“K”就是介电常数,Low K就是低介电常数材料。Low K技术最初由IBM开发,当时的产业大背景是——随着电路板蚀刻精度越来越高,芯片上集成的电路越来越多,信号干扰也就越来越强,所以IBM致力于开发、发展一种新的多晶硅材料。IBM声称,Low K材料帮助解决了芯片中的信号干扰问题。而Intel的目的是使用低介电常数的材料来制作处理器导线间的绝缘体。这种Low K材料可以很好地降低线路间的串扰,从而降低处理器的功耗,提高处理器的高频稳定性。

下表为几种材料的相对介电常数:

材料/比较项目 Low k SiO2 CVD* SiO2 High k

相对介电常数 2.50 3.80 4.50 25.00

* SiO2 CVD 代表等离子CVD方法制造的SiO2材料

在技术应用中,Low K材料最先出现在ATi的9600XT中。CPU方面,Prescott是Intel第一款使用7层带有Low K绝缘层的CPU,同时使用了Carbon-Doped Oxide(CDO)(最新的低介电常数CDO绝缘体)绝缘体材料,减少了线到线之间的电容,允许提高芯片中的信号速度和减少功耗。

Low K目前最大缺点是实际应用效果不明显,需要新的材料的介入,比如从有机材料领域寻求发展。Low K材料的开发速度可以说是空前迅猛的,前景光明,不过还是需要注意一些老问题,比如工艺不成熟、铜互连技术缺陷还有良品率问题等。此外目前的Low K材料可靠性还不高,不很耐高温并且比较脆弱,nVidia就已经指出Low K材料的易碎性。

(3)应变硅技术

晶体管的结构也将有所改变。不过不是在数量上,通道的长度将从60nm下降到50nm,而其他东西则保持不变。实际上其他的东西都是由通道长度决定的,不论是晶体管的速度还是大小。为了保证有利因素发挥同时减小负面因素,Intel会在应变硅(Strained silicon)以及新型的铜和含碳二氧化硅互连的低温介电体上使用开始使用90纳米技术。这个氧化物薄层非常的薄,仅有1.2纳米厚,完全符合上面提到的厚度为通道长度的1/45,却超过了Intel自己宣称的2.3纳米的极限值。

应变硅的使用目的和二氧化硅层相反,它是作为电子的屏蔽出现的,在其下的通道则是电子由发射端到接受端的路径,电流越高,电子运动就越容易,速度也越快。通道一般是用硅制成的,不过在使用应变硅之后,就需要将原子拉长,那么电子在通过稀疏的原子格时遇到的阻抗就大大下降。Intel宣称只需将硅原子拉长1%,就可以提高10-20%的电流速度,而成本只增加了2%。

(4)Terahertz晶体管与High K & DST

在未来Intel会怎样继续发展下去呢?首先,他们一定会榨干硅晶体管的最后一分“油水”,将其称作Terahertz晶体管(Terahertz就是1THz,也就是1000GHz)。目前Intel已经做出了15纳米晶体管的样品,很显然这种晶体管将带来巨大的功耗、发热量和电流泄漏,如果没有什么技术改进就毫无实用价值。

做出Terahertz晶体管首先需要使用不同的原料,因为他们决定了晶体管的基本特性。二氧化硅作为门和通道之间的绝缘层已经不适合,而需要用到Intel称为高K门电介质(High K gate Dielectric)的材料,Intel宣布已经完成了对High-K金属门电路晶体管技术的研发。这种材料对电子泄漏的阻隔效果是二氧化硅的10000倍。这项技术也通常被简写为“High K”技术,我们有必要做简单了解。High K的全称应该是High K金属门电路晶体管技术,它是由Intel负责研发的下一代CMOS晶体管的门电路部分。它采用高介电常数的材料,以达到更高的单个晶体管容量。容量大则意味着转换周期短,这意味着晶体管速度将更快,同时功耗比传统的CMOS晶体管降低很多,Intel说的100倍不会是夸张,在现有工艺水平前提下功率可能只会有20-80倍的降低,但是在45nm技术运用后,100倍以上决对有可能!这意味着采用High-K材料晶体管的处理器,在发热量方面将有很大优势。

第二个关键是称为耗尽型衬底晶体管(depleted substrate transistor,DST)的技术,实际上就是SOI技术的变形。Intel一直对SOI技术抱着怀疑的态度,如果没有什么重要的理由他们是不会使用这项技术的。Intel认为使用完全耗尽的通道没有任何好处,这个通道会变得非常的小,大约10纳米左右,这是很难制造的,同时也因为发射端和接受端的距离减小急剧提高了外接晶体管的阻抗。

因此DST技术就被推出了,相比SOI技术其做了一些改动来消除它的主要缺点,通道非常的短,同时也做了完全贫化处理。在一定的控制下驱动电流可以立即在门(晶体管门)通过,并不会电离在绝缘层下通道的任何部分。另外,这样也可以表现出虚拟通道增长的效果,从而体现出浮点晶体管的特性。

不过这只相当于在一个通常的SOI晶体管上使用了完全耗尽通道,主要的问题仍然是外接晶体管陡然增加的阻抗上。所以,Intel不会让通道的长度影响到DST晶体管上的漏极和接受端的长度。Intel通过降低关状态电压有效的将产品工作电压降到了1.0V以下,并表示可以在2010年达到0.6V。

上面技术的两项技术,(High k)高k门电介质和(DST)耗尽型衬底晶体管就是为了适应Intel的Terahertz晶体管而开发的,Intel宣称其可以做出32纳米的晶体管(15nm的通道长度),0.75V电压和1THz运行频率。

(5)来自AMD的努力

AMD也在HiP8中使用SOI技术,而不像Intel那样只准备用在1000Ghz的晶体管上。从理论上来讲,这样做同时也会伴随着晶体管外部阻抗上升到一个目前无法接受的程度。不过AMD已经做好的准备,我们很快就讲见到更快频率的晶体管。从以往的经验我们可以知道,新的晶体管将使得性能增加20%,同时还将降低泄漏电流和门极宽度。

AMD也在计划着未来,他们计划用高K值的金属硅酸盐(metal-silicate)绝缘材料取代目前的二氧化硅,这样将使得泄漏电流下降100倍,而不像Intel说的可以达到10000倍。

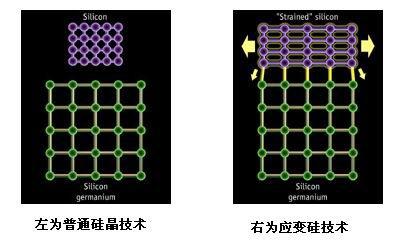

同时,AMD还计划使用SiGe(锗化硅)来取代纯粹的硅作为驱动电流的通道,和Intel在90纳米制程上采用的应变硅有些类似。不过下面这个物理现象将不能忽视:硅晶格会根据下面的元素的晶格调整自己(在这里就是锗了),并将延展一些。根据IBM的说法,这样潜在的阻抗将会比普通的硅下降70%,而晶体管性能将提高35%。

4、晶体管的革命,Intel VS AMD

传统的晶体管架构已经在微电子学使用了将近40年:经典的晶体管包括1个可以控制的电极和在它下面的电流顺序通过的另外两个电极。就这样,晶体管架构呈现出一种二维的状态。

普通晶体管结构和普通晶体管显微结构:

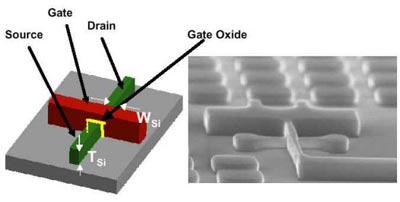

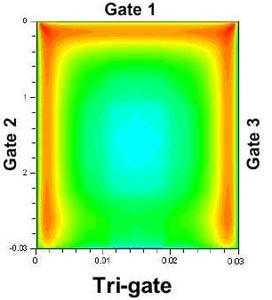

(1)Intel的三门晶体管

Intel在90年代末提出了新一代晶体管架构——三门晶体管。因为集成了众多的晶体管,同时还有着多重的门和通道,因此在微电子学领域,CPU被定义为一种三维架构。三门晶体管就是在单个晶体管内集成三个通道。

三门晶体管就是在单个晶体管内集成三个通道。从微观上看,三门晶体管的门(gate)和发射器(emitter)和收集器被设置在了普通晶圆的表面,并且他们之间相互交叉。这样就构成了一种有趣的结构:门电子束的截面是一个矩形,顶端和两侧都是门电极,这样一来,三门晶体管就像是反转的传统晶体管树立在了晶圆上。

传统的晶体管架构呈现是一种二维的状态,包括1个可以控制的电极和在它下面的电流顺序通过的另外两个电极。普通晶体管只在顶端有一个门电极,也就需要更多的时间在通道上切换充电状态以改变晶体管的开光状态,同时也需要更高的电压。

而通过三门晶体管技术,理论上只需要有几束相同的电波,我们就够通过使用极限的电压打开晶体管,几乎同时门会被出现在所有电波上的电流所阻断。所以通过晶体管的总共电流等于每个交叉点的电流的和。假设我们有6个输出,其中三个发射器,三个接收器,那我们可以得到与普通晶体管相同的电流,但相同情况下所需要输入的电压量却要低3倍。或者相同的电压可以驱动3倍于以前的电流,总体效率将提高20%,这便是三门晶体管的魅力所在。而且三门晶体管的高效性降低了对通道长度的要求,可以大大降低对生产技术的要求。不过这项技术目前还停留在实验室阶段,还没有在Prescott上应用,有望在2010年前开始实际应用。

当然,制造这样小的晶体管当然需要更为先进的蚀刻技术来支持。目前Intel仍在使用旧的248纳米设备来制造90纳米的芯片,当然有些关键部位是由193纳米设备完成的(大约占20%)。在完成了向193纳米设备的过渡之后,Intel就可以轻松一下了。这些设备可以一直用到65纳米晶体管芯片的生产。

在此之后,EUV(Extreme Ultraviolet,极端远紫外光)光刻技术将开始发挥。EUV与传统的紫外线蚀刻技术是一样的,都是将激光通过掩膜,把掩膜上的电路图转移动晶圆之上,不过EUV设备使用的是134埃波长的激光,采用部分波长极短的电磁频谱,因此能实现更小的蚀刻尺寸。Intel已在2005年开始使用EUV技术,同时开始45纳米制程的芯片生产了。

(2)AMD的双门晶体管

AMD也在考虑多门晶体管,特别是双门的,这也和Intel喜爱的三门晶体管不同,没有上方的控制电极。AMD的这种鳍式场效晶体管(Fin Field-Effect Transistor,FINFET)也就比Intel的更高一些,同时发送/接受电子束也要窄一些。该晶体管的宽度大约为门极宽度的1/3,这在光刻技术可以引起一些问题,同时也是少数的“小”而不“好”的情况之一。不过不管怎样,FINFET和其他的三维晶体管一样,相对于传统的晶体管都有很多的优势,特别是它缩小了通道长度。总的说来,AMD在手上有足够的筹码来回应Intel的1000GHz晶体管和三维晶体管。目前AMD已离开摩托罗拉,转而和IBM加强合作,HiP8成为AMD和摩托罗拉合作的最后一项技术。

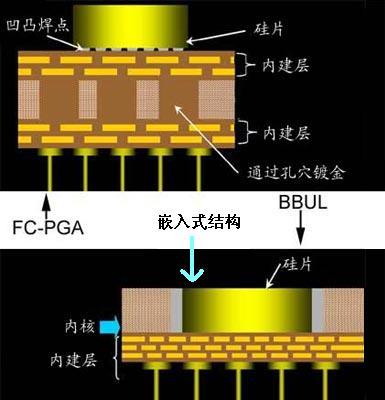

(3)新型封装,势在必行

有了如此先进的制造技术,自然需要坚实的基础。好马配好鞍,面对日新月异的生产工艺,新型封装势在必行。BBUL(Bumpless Build-Up Layer,无凸块增层)封装技术早在2001年10月份就对外披露,当时Intel宣称这项技术为“未来微处理器设计”,准备在5到6年之内投入使用。它将会成为未来65nm、45nm时代最流行的封装技术。据称,这项封装技术可以让CPU在未来6年的发展道路上高枕无忧,因为它能使CPU内集成的晶体管数量达到10亿个,并且在高达20GHz的主频下运行。

传统的FC-PGA工艺是:CPU核心与基板彼此分开制造,封装时将CPU核心放在基板中央的预定位置上,并通过微细锡球(tiny solder balls)将它们焊接在一起,CPU核心自然就位于封装的最上方。

BBUL如上图。它通过取消这种中间的微细锡球,将裸晶(Die)直接放入封装基质中,从而把组成一个处理器(诸如Pentium 4)的6~7个金属层减少大约3层,使处理器的厚度达到只有1mm。Intel声称,利用这项新技术,基本上可以把一个封装包看作是围绕着硅核“生长”起来的,避免了损害芯片效率的焊接过程以及影响硅核性能的溶化步骤。由于数据的必经之路缩短了,新的封装技术会帮助提高芯片的整体运算速度和性能。BBUL封装的结构中,CPU内核看起来就被深埋在内部,这样就避免了繁杂的焊接过程以及影响硅核性能的熔化步骤,让CPU核心可以更直接、更贴合地与基板连接。

BBUL封装的关键在于芯片直接放入封装中,这样处理器的高度被大大降低,封装也轻了不少,对于移动设备也更加适用。BBUL增强了在单一封装中设计多个硅元件的能力。与目前FC-PGA的一体化封装方式不同,BBUL技术可以将两个CPU核分别封装,这样可以避免在生产时即使只有一个核出现问题就要扔掉整个处理器的窘境,对于更多核心的处理器来讲,节约的成本将是可观的。尽管在未来4~5年内BBUL技术才有可能真正实用化,但其为处理器设计和制造所带来的影响将极其深远。

还有值得重视的一个优点:由于省去了焊接的Bump(电极),使硅核和封装基层一次生成,在降低能耗的同时提高了处理器的稳定性。初步估计,BBUL将比目前的封装方式降低25%的能耗,进而可减少高频产生的热量。

5、存储器编译器的升级

根据Emerging Memory Technologies公司的稿件,在器件从90nm工艺节点向更高密度工艺发展的道路上,同时支持1T和6T存储器的新一代存储器编译器与测试和可制造性工具及高质量存储器的紧密链接,可使架构师充分地利用数十亿的晶体管规模,从而续写摩尔定律。

Gordon Moore在1965年就曾预言集成电路规模每年将翻一倍,他还预言1975年会出现内含65,000个元件的单芯片器件。现在,移动设备存储卡所用的每个芯片包含的晶体管数量已接近100亿个。虽然对用户来说运算功耗成本一直在按摩尔定律下降,但制造商的成本却是相反的趋势。设计世界一流的系统级芯片(SoC)器件的实际成本在每次工艺升级时都会翻倍上涨。新器件复杂性的提高是成本上升的主要原因。

对SoC架构师来说,复杂性和成本并不是唯一需要考虑的因素。功耗在不断发展的半导体工业中又成为重要问题,你愿意拥有高性能的手提电脑而只能运行于“电池模式”,或是手持先进的掌上设备,却时时发愁剩余的电量。因此电池寿命和功耗逐渐成为主要的设计焦点,并迅速替代速度成为人们追求的另一目标。

同时随着集成电路设计变得越来越复杂,成本也在不断提高。一个采用先进的90nm技术设计的2,000万门SoC成本大约为2,500万美元,需要140位硬件设计师和170位软件设计师。即使有了这些大型团队,设计周期也是相同的,或比前几代有所减少。上市时间将成为市场表现的主要差异,将直接关系到产品的利润空间。

新一代存储器编译器将会解决这些问题。SoC架构师在定义目标集成电路时,需要评估和比较许多潜在配置。可以用优秀的现成EDA工具定义不同抽象层次的逻辑。为了正确评估包括存储器在内的整个系统性能,架构师需要知道不同配置下的存储器行为内容。这一问题的解决方案对1T高密度存储器和传统的6T SRAM存储器来说都是一样的,即用存储器编译器为上千种不同的存储器配置提供精确的面积、性能、时序和功耗评估。

新一代存储器编译器增加了以往只用于定制存储器配置的功能。基于激光-熔丝的修复、内部误码检测和纠正(ECC)、同时支持1T和6T存储器阵列等就是存储器编译器带来的一些功能例子。随着SoC设计复杂度的提高,这些集成电路的价值也在与日俱增。达到最佳的良品率优化变得越来越重要。为了获得良品率分析所需的测试信息,必须配置BIST控制器,并使之与存储器编译器一起工作。必须将面向完全存储器阵列可视性的修复策略、列扰码或ECC直通模式等细节从存储器编译器传达给BIST编译器,从而使存储器模块能在最终SoC设计中得到有效完整的测试。

6、小结

让我们简单回顾一下:提高晶圆尺寸和提高蚀刻精度可以让CPU容纳更多的晶体管,同时也维护着摩尔定律。但在0.18mm工艺后,由于漏电等其他原因引起的功耗、发热等因素,让单纯提高这两项工艺没有实际价值。

紧接着,一次次的技术革新开始了,各大公司开始研究新技术、新材料,提出新的解决方案。SOI技术将在90纳米以及更细微的制造技术上发挥作用,来缓解泄漏、提高晶体管性能。芯片互连层将由Low K材料完成,门和通道之间的绝缘层将由High K材料完成,它们能有效提高电气性能。新的元素(如诸元素)将会使晶体管的性能进一步提高。为了承载未来的CPU,新的封装技术也蓄势待发。未来还将改革晶体管结构。

以上就是当今CPU的生产工艺概述及展望,这些激动人心的技术是芯片产业在摩尔定律的引导下不断创造、发明的;同时它们也支撑着摩尔定律奇迹般地跨越了一个又一个障碍,形成相辅相成的关系。

但由于CPU架构障碍,处理器成倍增加的晶体管数量并不能转化为成倍增长的性能。从现在的情况开来,摩尔定律将会在某一天失去作用,已经有人认识到了这一点,并开始谈论如何对处理器架构进行彻底的改进,这是一件令人高兴的事。CPU性能的增长也不能永远依赖增加晶体管数量,其架构设计也是当今芯片产业的一个热门话题。下面,我们将关注重点转移到这里,让理性的分析再度引导我们走进各种CPU架构。

1、一款架构引导一代产品

一款架构引导一代产品,这是CPU产业中的规矩,也是一种很合理的发展方式。当我们对不断提升的频率感到厌烦时,一款新的架构又能再次引起人们的注意。一般来说,新的架构有以下几个优势:采用新工艺、新技术(指令集等),有利于提升主频、降低功耗、降低生产成本。新架构的提出让我们看到了新希望,但也同时牢牢套住一代产品的发展路线。我们很容易预测出这个架构下产品的性能增长线路,如果平时关注生产技术,我们还预测出这个架构的生命有多长。再加上以往的经验,我们可以知道它是否是一款过度架构,它带出来的产品是否值得购买。

下文将从各方面介绍现在市场上的3中架构Pentium 4、Pentium M、Athlon 64。然后将提出一些CPU设计中的优秀技术,比如多核心,PARROT等。

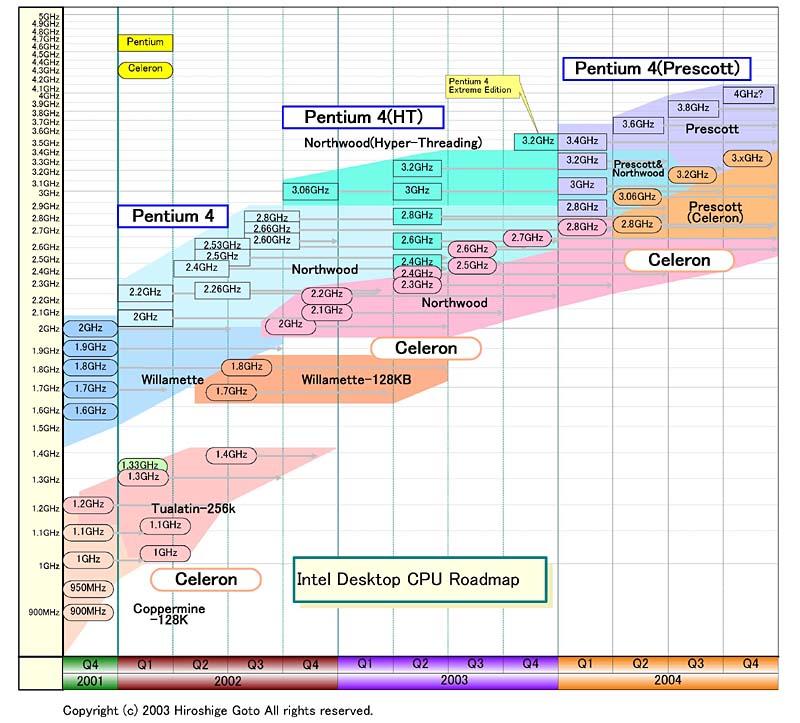

(1)Pentium 4架构

作为全球出货量最大的一款CPU,我们没有理由不把它放到第一的位置讨论。Intel其实早在1998年就开始筹划Pentium 4的研发工作了。但由于这是一个创世代的伟大架构,于是在2000年11月20日才正式发布。

Pentium 4包含三代核心,Willamette、Northwood和Prescott,它们统一于一个架构——NetBrust(网络爆发)。这个架构是以前不敢想的,它的特性是拥有冗长流水线以带来较高的频率,Willamette和Northwood用到了20级流水线,Prescott则达到了31级,它们的最高频率分别是2.0G、3.4G和3.8G。按照Intel当初的预测,Pentium 4在NetBrust的带领下能达到10GHz的频率。

NetBrust流水线过长,造成了单位频率效能低下,高性能要有更高的频率保证,而这一要求就转嫁到生产工艺上。联想到前面我们讲到的Intel一个又一个的新工艺,我们可以确定,采用NetBrust是Intel当初过分自信的结果,也是它为了维持摩尔定律而对未来估计不足的结果。最后一颗Pentium 4是Prescott 3.8G,它没有达到Intel当初的豪言壮志,甚至连原计划的4G也没能够得着。

图为Intel桌面级CPU的路线图,我们看到很多产品没有按时发布,并且实际产品没有达到当初的预计水平。

Pentium 4也有一些相当前卫的设计,比如我们熟悉的追踪缓存结构,四倍速QDR技术等。因为Pentium 4的流水线长达20级,每一级分配到的计算工作量相对于以往的CPU更少,所以处理速度更快,这也就带来了CPU频率的提高。但是超长流水线带来的负面效应不得小视,就是分支预测的效能下降——如果有一个分支预测出错,那么整个任务得从计算流水线头部重新开始执行。这对于CPU是致命的打击,因为分支预测出错是计算过程中常有的事,流水线短的CPU能有效缓解这个问题,性能消耗不大,但拥有冗长流水线的NetBrust架构受不了这个。

为此,Intel把一级缓存的数据缓存(I-Cache)和指令缓存(D-Cache)分开,把(I-Cache)剥离出来,单独形成Trace Cache(追踪缓存)。它的容量只有21KB,位于指令解码器和内核第一级计算流水线之间,作用是存储指令解码器产生的微操作,以备流水线出现分支预测出错时直接调用,无须要求解码单元再次捕捉相同指令并加以解码。这种结构的使用很大程度上降低了分支预测出错对CPU的威胁,称得上是一个成功的设计,但它也是在当时的情况下逼出来的技术,它的作用也只是缓解压力和增强效率。Intel在NetBrust架构中添加了追踪缓存,另Pentium 4的表现没有让人太失望。QDR技术在系统总线上同时传输4个不同的64位数据流达到了4倍速率的效果,所以我们看到Pentium 4的外频是200MHz而前端总线却是800MHz,数据吞吐量明显增大。这两项设计在Pentium 4架构中一直沿用至今,是Pentium 4的顶梁柱。HT(超线程技术)是在Northwood时代开启的,它当初被寄予厚望能显著提升CPU效率,最大程度消耗高频CPU浪费掉的资源,特别是在CPU繁忙的多任务模式下,传说有30%的性能提升。这是一项相当好的技术,但用在Pentium 4上最终效果不大。

Intel早已发现NetBrust架构的缺陷,并在Prescott上全力弥补,这些弥补都是在分支预测的改进方面。首先是增加了TLB(变换索引缓冲区)的入口数量,因为CPU要读取内存时要从TLB中调用虚拟地址到物理地址的映射,而且调用的命中率几乎在99%以上,Prescott具有128个TLB缓冲,是Northwood的2倍。随后又增加了ITC(指令追踪缓存),Prescott比Northwood多30%的ITC面积,可以追踪多达4096条虚拟地址,又是Northwood的2倍。在FBTB(前端分支目标缓冲)方面,精确到了4路48bit,而Northwood则是4路32bit。而且Prescott的FBTB还可以包含预测信息,每一个信息都可以用2bit的位宽维持16个双峰计算结果。这2bit可以表示为:0=不被采纳,1=大概不被采纳,2=或许被采纳,3=被采纳。这是一种相当先进的预测信息。在总体地址线上Prescott使用了48bit虚拟地址,因为在内存管理中,虚拟地址可以表示比物理地址更为宽广的范围,这个位宽已与当时最先进的AMD K8核心相同。所有这些都是在核心上的重大改进,它们共同协作帮助Pentium 4增加分支预测的准确性,但结果不是很明显。

Pentium 4一向以高频率、高功耗、高发热著称,原本不应该这样。因为按照预计,先进的生产工艺完全满足Pentium 4架构的需要,但现在看来,Pentium 4是一个对生产工艺要求相当高的架构,Intel拼命努力还是没有满足它的胃口。当然我们不能以这些劣势来埋没Pentium 4的功绩,Pentium 4仍然是活跃在市场上生命力相当强的CPU。但不可否认的是曾辉煌一时的NetBrust架构现在事实上已成为Intel为自己设置的枷锁。

(2)Pentium M架构

在Pentium 4架构饱受非议的同时,Intel移动产品线上活跃着一个设计优秀又有潜力的架构——Pentium M。Pentium M的卓越表现得益于它没有采用长流水线设计,虽然在前端总线、接口方面与Pentium 4类似,但Pentium M实际上是在Pentium III基础上发展的。

Pentium M的流水线只有12级,这种保守的设计让它能够保持优秀的指令效能和较低的功耗水平。此外,Pentium M吸收了大量来自NetBrust架构的研究成果:其一、引入了QDR-speed四倍速前端总线技术,实现400MHz/533MHz前端总线运作,更宽的总线有效增加了数据流量;其二,引入Mikro-Op-Fusion堆栈管理技术。Mikro-Op-Fusion是一个复杂的硬件堆栈管理器,它能够大幅改进分支预测的效率。

在缓存方面,Pentium M的设计明显优于Pentium 4:Pentium M拥有64KB一级缓存,指令(D-Cache)与数据(I-Cache)分开独占32KB。区别于Pentium 4的追踪式缓存结构,Pentium M一级缓存不仅容量占优,且使用了Write-back(回写)模式,效率比Pentium 4采用的Write-through(直接写入)模式更高,存取时间也大为缩短。而且,Pentium M的二级缓存采用了8路联合的运行模式,每路又被划分成4个功耗区域,在专门的堆栈管理技术控制下,可以在CPU运行中关闭用不到的功耗区域。在任何一个时间片内,只有1个功耗区域处于激活状态下,其余部分的功耗几乎可以忽略不计。另外,Pentium M还采用了Intel第三代SpeedStep技术,支持以1MHz为单位的无级平滑变速,在节能方面更领先。

综上所述,较短的流水线、低功耗缓存、取自NetBrust架构的最新成果以及先进的生产工艺,使Pentium M成为CPU设计史上的一个经典。而Pentium M在性能方面也没有另人失望,它始终于同一时代的桌面产品保持同步。到目前为止,Pentium M家族中最高性能版本是Pentium M 770拥有2.13GHz主频、2MB缓存,它与3.46GHz的Pentium 4 XE性能相当。形成鲜明对比的是,两者的最高功耗分别是27W和135W,晶体管的规模则分别为1.4亿和1.78亿。

无论从哪个角度来看Pentium M在架构上都优于Pentium 4,作为低功耗产品Intel让Pentium M架构担当移动产品也无可厚非,但是不是有点大材小用了呢?再补充一点,Pentium M架构是Intel在以色列的海尔法的CPU设计团队开发出的,这个实验室还提出了一项技术——PARROT,我们后面马上要做叙述。

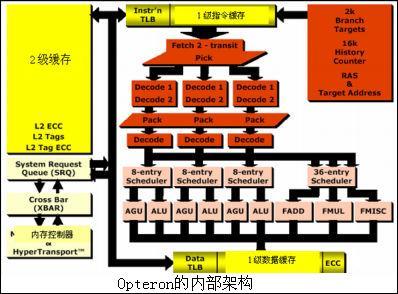

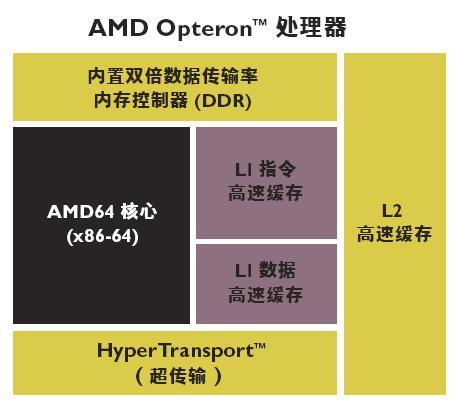

(3)Athlon 64架构

这里我们以AMD Athlon 64架构最具竞争力的高端代表——Opteron来做说明。

a、设计新型流水线

首先要明确的是Opteron微架构设计的首要目标是为用户提供新一代的性能。提供这一性能必须平衡两个方面:一是更高的时钟频率。

二是更高的IPC(单位时钟性能)。

达到更高的时钟频率必须有更长的流水线。从技术上来看,CPU厂商大都通过增加流水线级数(“超长流水线”)来实现工作频率的提高,当然AMD也不例外。增加流水线级数以后,各级的处理负担就会减轻,工作频率也容易提高。

AMD64的流水线前端指令获取与解码逻辑标识被精简,提供从解码器到执行管道调度程序间更大的指令打包程度。为适应这一改变,设计中重新定义了管道分级以保持高度的频率可测量性,结果比第七代微架构多出两个管道分级,AMD的Opteron最终产品拥有12级整数运算流水线和17级浮点运算流水线。长流水线可以带来较高频率,但流水线过长反而会影响CPU性能。为此,AMD只有用新技术来弥补长流水线降低的IPC。为了不使过长的流水线影响到分支预测的准确性,Hammer核心在分支预测失误之前流水线中可以容纳更多指令数。为了充分利用这个优势,AMD需要一个更大的缓存来储存这些指令。AMD这次采用宽流水线,并填充了大量指令,就是为了降低分支预测失误的机率,在提升频率的同时提升IPC。

b、集成DDR内存控制器

为了彻底铲除CPU与内存间的瓶颈,尽可能减小内存到CPU的延迟时间,AMD把以往北桥芯片中的主要部分——内存控制器内建在CPU中。我们知道内存中的数据被调往CPU要经历多个环节,其中内存到芯片组的速度和芯片组到CPU的速度是产生延迟的罪魁祸首,已有过许多芯片组因为设计失误导致延迟过长而降低性能。许多测试也表明Opteron的延迟时间表现很出色。集成DDR内存控制器看似简单,其实更重要的一个作用是在SMP架构中建立高效的内存读取机制,这正是Opteron中SMP架构的精髓(下文将提到)。实测表明,集成内存控制器使Opteron系统的延迟大幅度低于Xeon、高频P4等系统。同时这项技术可以简化芯片组的设计,nVidia支持AMD64位CPU的nForce3芯片组已省去了北桥芯片,成为单芯片芯片组。

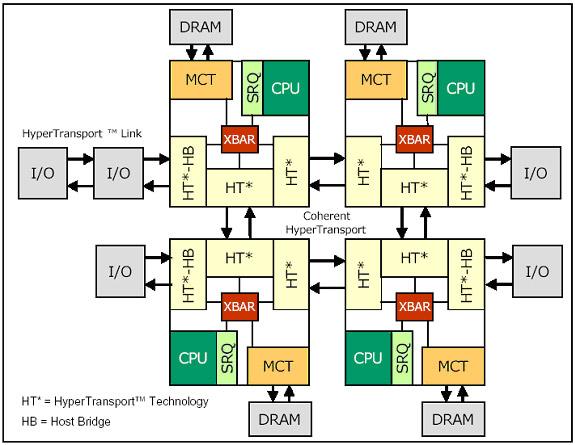

c、HyperTransport总线

HyperTransport(简称HT,超传输),是AMD为Hammer开发的一种双向的“点对点”高速数据传输总线,运行于处理器与芯片组或芯片组间其它部分的连接中。在SMP架构中,处理器间也是通过内建额外的HT控制器进行连接的,AMD将这称为“glue less”(免中介)方式。HT本身具有很多的优点:高速、低延迟时间、结构紧凑。该总线最大可以提供6.4GB/s的带宽,通过简单的设定总线位宽(2位到32位)和工作频率(400MHz到1600MHz)来灵活改变总线的带宽(100MB/s到6.4GB/s)。每个Opteron处理器都将集成3个HT控制器,要这些多余的总线又有什么用途呢?答案是建立多处理器系统。图中一个大方框表示一个CPU,CPU之间用HT连接。HB表示CPU内置的桥接芯片,它与外部I/O设备也用HT连接。在这种方式下,2路(或多路)SMP架构的系统配置便不再依赖于芯片组的支持,双处理器平台的成本会大幅下降。

此外,与K7结构相比Opteron拥有更为出色的TLB结构,Opteron微架构增多了TLB入口的数量。通过把全局历史计数器中双峰计数器的数量增至16K(是K7的4倍),Opteron处理器加强了分支预测功能来提供更高的性能,特别是在较大的工作负荷中。

Athlon 64架构可以说是AMD与Intel对抗中的一员大将,也是AMD设计最成功的架构之一。正是凭借优秀的架构设计,AMD以一个小厂商的身份成功抗击着Intel这样的超级大厂,也正是因为它的存在,我们没有看到一个CPU界的微软。

2、CPU设计中的优秀技术

(1)多核心技术

当消费者还在享受着CPU主频提升所给我们带来的急速快感时,Intel和AMD两家公司却不约而同的感受到了继续按照摩尔定律提升CPU主频的困难。Intel于去年10月份宣布了取消4GHz奔腾4处理器的开发计划,AMD也表示其高端Athlon FX57将是很长一段时间内主频最高的产品。究竟是什么原因使得频率提升如此困难?首先,目前CPU单纯依靠提升主频已经很难大幅度提升CPU的性能,从而减缓了消费者对高频CPU的需求;其次当CPU主频达到2GHz以上的时候,处理器功耗也达到了近100W,这已经是目前风冷散热技术的极限,很明显单核CPU在主频提升乏力的情况下已经显得力不从心。

“多核心CPU解决方案是摩尔定律发展的必然产物,”Intel分析员Nathan这样说道。多核心技术是以后的发展方向,也是当今最热门的技术。

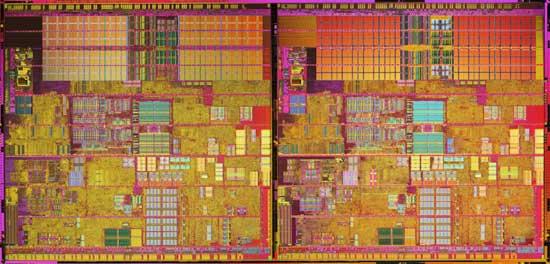

所谓多核心,多核CPU技术是在同一个硅晶片(Die)上集成了多个独立物理核心,在实际工作中多颗核心协同工作,以达到性能倍增的目的。最早提出多核心CPU想法的人或公司现在已经无从考究,但对此表现最积极的属SUN、IBM和Intel。它们联手开发多线程微处理器和多核心微处理器,并且已经取得了一定的成果。IBM公司的Power4芯片首先使用了2个独立的处理核心,高端的Sun Microsystems也使用了多核心的处理芯片。Intel即Itanium2之后,公布了代号为Tanglewood的下一代Itanium发展计划,其中这款全新的Itanium芯片最高将包含16颗独立的处理器。加上超线程技术,这款处理器能够处理高达32个线程!不能不说十分的惊人。

多核心技术在应用上的优势有两个方面,一方面是为用户带来更强大的计算性能,更重要的一方面则是可满足用户同时进行多任务处理和多任务计算环境的要求。

图为Intel的Pentium Extreme Edition 955内部结构图,可以很清楚的看到在一个CPU内有两个完全相同的内核。对于多核心CPU的功耗问题,IBM最近发布的一项称为“eFUSE”的芯片调变技术,应用了该技术的芯片能够根据运算任务的多少打开或关闭芯片中的另外一个备用的处理器内核,从而让多核心CPU在性能和能耗方面有更好的表现。

多核心CPU的实现看似简单,但Intel与AMD却在技术方面分道扬镳。

从集成的角度来看,业界通常把多处理器计算机系统分为“紧耦合”和“松耦合”两种形态。一般我们将通过将多台计算机组成集群(Cluster)的方式来增加计算机系统处理器数量以提高计算性能的做法就是一种相对比较宽松的耦合。这样的计算机群有各自独立的CPU、内存、主板和显卡等周边配件;而通过SMP(对称多处理器)架构来增加处理器数量的方式就是一种紧耦合,比如一板双芯的方式就是一种比较典型的SMP计算机耦合方式。假如,我们将2个处理器放在一个芯片内,或者一块基板上,这就是一种更加紧密的耦合状态,业界将它称为CMP(单芯片多处理器)架构。简而言之,AMD和Intel新推出的双核心处理器都符合CMP的逻辑架构,他们之间并无详细的区分。

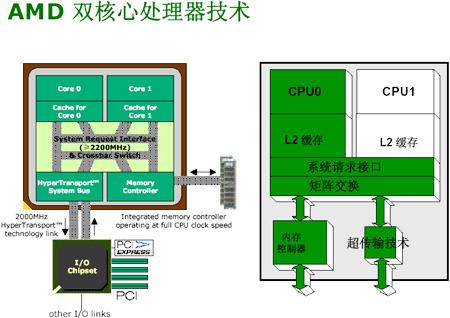

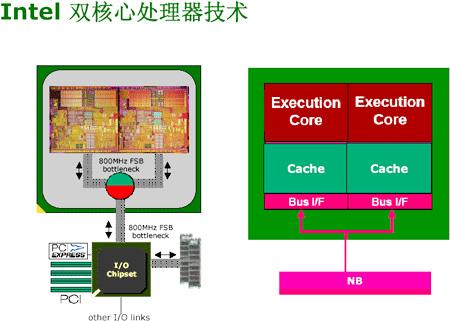

下面给大家带来的是AMD和Intel双核CPU技术示意图:

AMD Athlon64 X2处理器与Intel双核P4的最大不同在于仲裁通信系统的位置。AMD的双核心技术使用的是一种特别的架构,AMD内部称其为Direct Connect architecture。与Pentium D相比,它增添了“系统请求接口”(System Request Interface,SRI)和“交叉开关”(Crossbar Switch)。它们的作用是对两个核心的任务进行仲裁、及实现核与核之间的通信。AMD的两个核心会把请求放在系统请求对列(SRQ)中,当资源允许的时候,会把任务分配给合适的核心去处理,整个过程都在CPU内部完成,系统性能也就此大大提高。同时也可以让每个核心都有独享的I/O带宽、避免资源争抢,实现更小的内存延迟,并提供了更大的扩展空间,让双核能轻易扩展成为多核。而Intel的双核产品就没有按照这样的思路来进行设计,它们将任务分配控制单元和仲裁单元从CPU中脱离出来,放在北桥芯片中。因此Intel的双核处理器也被称为是“两颗处理器在一条前端总线上的简单复合”。

AMD认为Intel仅仅是将2个完整的处理器核心简单的集成在一起而已,它们非但没有直接受到任务仲裁器的控制,而且还同时连接到一条带宽有限的前端总线上。这样的设计架构势必会造成2个处理器核心单元抢夺总线资源,从而影响性能。

AMD当初坚持将内存控制器整合在CPU中,就是出于“距离越短,速度越快”的原则,从而降低延迟,提高系统效率。但是,Intel自信自己的芯片组系统可以提供足够的带宽支持,即便将Pentium D的任务仲裁单元外置在北桥中,对于双核处理器的系统来说造成的延迟和性能损失也是微乎其微的。

看完了AMD与Intel的内部争执,让我们听听来自一个重要人物对多核心CPU的不同意见。nVidia的首席科学家David Kirk近日在斯坦福大学举行的最新芯片技术研讨会(Hot Chips conference)上说:CPU的多线程技术和多核心技术给现在的程序开发带来了很多困难。Intel、AMD这样的CPU制造商所使用的多线程和多核心技术,看起来好像是使CPU的性能加倍,但是从本质上来说,并不能解决CPU主频提升以及制造工艺的瓶颈,而多线程、多核处理器的出现对于游戏开发人员来说也形如鸡肋,并不能从第二个核心中得到任何受益。多核CPU乃黔驴技穷之作。

不论怎么样,AMD与Intel都在2005年完成了多核心CPU并成功在市场上发布,取得了不错的效益和回应,虽业界还存在不同意见,但这项技术在未来必将发扬光大从而普及。又因为摩尔定律遭遇挑战,半导体工艺面临绝境,单芯片设计在性能上持续提高成问题,故双核乃至多核的CPU结构将会流行起来,类似于XBOX的PPU,CPU,GPU三芯片设计,处理器的逻辑结构可能会走上这种道路。到时一个CPU的几个核心可能会更针对应用而开发。比如Pentium M的逻辑结构为移动计算而服务,而至强则为服务器而优化。总之多核结构将是发展的趋势。

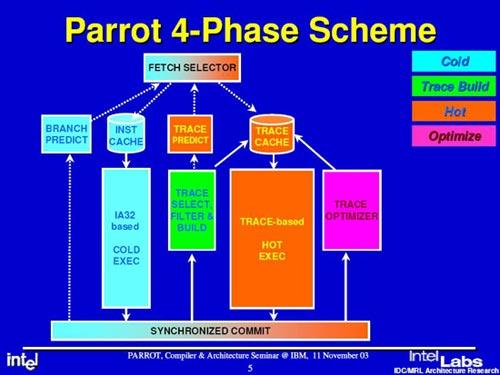

(2)PARROT架构

这是一个革命性的CPU架构,PARROT架构的提出标志着Intel以后的研究方向彻底转变!

与Pentium M一样,PARROT也是出自Intel在以色列海尔法的CPU实验室。早在2003年,该实验室的工程师们公开发表了一篇名为

“Power Awareness through Selective Dynamically Optimized Traces”(借助选择性动态优化线路实现功耗最优化)的技术论文。在论文中,研究者第一次提出“Power-Aware aRchitecture Running Optimized Traces”一词,PARROT架构也由此得名。

该论文提出一个新的构想:通过对动态执行线路进行优化,将能够大幅度提高芯片的运行效率,使得在单位功耗条件下可获得的运算性能得到大大提升。当然这个构想是根据著名的“阿姆达尔法则(Amdahl’s law)”,该法则出自IBM 360大型机的主要开发人员Gene Amdahl之手,它的关键点便是“在计算机编程的并行处理中,少数必须顺序执行的指令是影响性能的一个因素,即使增加新的处理器也不能改善运行速度。”

基于阿姆达尔法则研究人员发现优化CPU的执行结构成为提升顺序指令效能的唯一方法。他们还发现,20%的程序代码会占去80%的CPU动态执行资源,这类操作被称作Hot execution(热操作)的代码要比冷操作代码更规则、更容易预测、以及有着很长的不包含分支指令序列为前提。在传统的CISC处理器架构上,这类操作会频繁地让CPU前端(Front-End)的解码器和后端(Back-End)的动态执行调度单元经常地重复执行、传输同样的代码,消耗大量的电力。

为此,PARROT架构针对这些操作进行了优化设计,NetBrust架构中Trace Cache进行了革命性改进,对Hot-Trace采取渐进式的排列优化,并且重新引入L1指令高速缓存D-Cache(减少“冷操作”的微操作占用Trace Cache),让“冷操作”和“热操作”分别运行在不同的执行电路上,大而降低运算单元的等待时间(例如缓存的潜伏期),提高“热操作”的执行效率,以“减少执行一条指令或者某项工作所需要的单位时间”的观念来达到间降低耗电的目的。

可以说,引入PARROT设计理念的CPU架构中,热操作和冷操作拥有彼此独立的取指和执行单元,但根据“多劳多得”的分配原则,热操作被分配了更多的处理资源。这样设计所带来的优势是相当明显的:不但执行单元(HOT EXEC)更加强大,而且拥有冷操作所没有的单元,比如追踪优化器(Trace Optimizer)、追踪选择过滤&构建(Trace Select Filter&Build)等,通过实际贡献对CPU资源进行合理规划,这就是PARROT的巧妙之处。

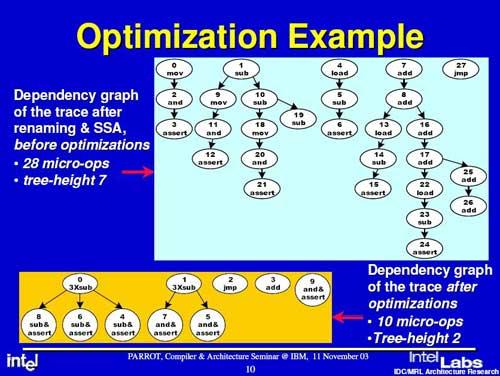

可以看出,这个不起眼的追踪优化器(Trace Optimizer)是PARROT架构在Trace Cache应用上的一大改新,也被认为是PARROT的精髓所在。从目前看到的资料,PARROT的追踪优化器几乎就相当于一个能对代码进行各种优化的小型硬件编译器。

在Intel的范例中,一个原先包含28个微指令、7层指令树,经过最佳化后,可以减少成10个微指令、2层指令树,无论对于改善Trace Cache的空间利用、提升Trace的执行效率、增强Trace Cache的微指令分派率(Dispatch rate)以强化IPC、以及减少实际上所执行的微指令数目,都有着立竿见影的效果。

Intel表示,原先4-Wide OOO的Merom核心,结合PARROT架构的方式以及加倍的执行单元数目,可以提升平均约45%的IPC。这将使Intel的CPU发展理论由“频率第一”转变为“效率第一”,使用PARROT架构意味着Intel接受了一个新的架构并准备大力发展它,同时也否定了自己在过去坚定执行的路线。但是按照通用的算法,新架构的性能只有10-20%的提高,PARROT架构真的有这么神奇,还要看以后的实际表现。

虽然在理论上PARROT架构可以极大提升执行单元的利用效率,但也有缺点:一个是将会大幅增加处理器的生产成本。要维持两个执行管线之间的同步化、以确保程序代码的正确执行顺序,就会大幅增加控制单元的复杂度,尤其是发生中断、例外等状况时必须迅速储存处理器状态的情形。另外一点,由于Trace Cache拥有比传统指令高速缓存更复杂的控制、预测电路,因此占用的空间成本要比指令高速缓存高出不少。这些因素除了大大增加设计的复杂程度外,也会给未来CPU的性能造成潜在的负面影响。

可以肯定,新的架构设计和对现有运算方式的优化将是未来CPU设计的发展方向。以更合理的方式换取性能的提升,特别是提高效率,也将成为CPU设计工程师永远思考的问题。

回到开头提到的NetBrust架构,它该何去何从?是保留还是舍弃?如果保留,该如何运用新技术发展它?摆在Intel面前的这些课题该由谁解决,透视现在的市场发展以及Intel的蓝图,以目前的观点看,来自海尔法团队的PARROT架构呼声最为强烈。从现在的产品路线看,一个全新的概念正在被Intel强调——Performance/Watt,性能功耗比。在2005,秋季IDF(Intel Developer Form Intel开发者论坛)上,Intel发布了其在2006年的处理器更新计划——放弃现有高耗低能的NetBrust架构。未来的新框架将接合以色列开发组的核心框架开发优势,在大幅提高性能的同时,降低功耗。最后观点:NetBrust已彻底被PARROT替代,Prescott成为NetBrust下的最后产品。从Intel新发布的Conroe核心CPU中我们可看到,它舍弃了NetBrust架构。Conroe只有14条流水线,效率比同频率下NetBrust架构Pentium D高40%以上。

HT超线程技术的废除也是PARROT架构引人注意的地方。因为PARROT的设计合理,冷管线和热管线都是处于高效率的运行状态,再也没有更多被闲置的资源可利用,HT自然不能发挥出它的效能,被Intel放弃也在情理之中。接下来的路对于AMD来说是非常难走的,在核心设计方面可能已经落后于Intel,以效率取胜的Athlon可能不是Conroe的对手。在工艺上,它又落后Intel一步,Intel的65nm的产品已经上市,工艺不断成熟。AMD还在沿用着90nm,如果不更新工艺用现在的路线发展,达到Conroe的水平功耗恐怕要超过150W,90nm还能用多久?

(3)虚拟技术

支持虚拟技术是当今CPU的一个重要特性。在这里我们有必要对它先做了解。

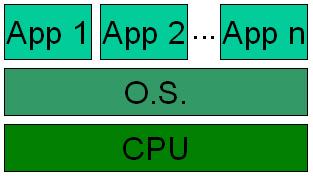

虚拟技术也不是什么新玩意,现在市场上的一些软件也能实现类似的虚拟效果。不过大家可能会被虚拟技术、多任务,以及超线程弄混淆,这里我们有必要解释一下。多任务是指,在一个操作系统上同时运行多个程序;而虚拟技术是指,你能在一个CPU上运行多个操作系统,同时又能在多个操作系统上运行多个程序;超线程是指,为了提高对称多处理SMP(Symmetric Multi Processing)性能,将一个物理CPU模拟成两个逻辑CPU,但是这两个逻辑CPU不能被单独使用。下面从上到下分别是多任务、超线程、虚拟技术的示意图(虚线框代表一个CPU):

如果CPU同时支持超线程和虚拟技术的话,同时运行的每个操作系统都认为获得了两个CPU,这样也能在每个操作系统中改善对称多处理的性能。

在虚拟技术下有两种工作模式:根(root)模式和非根(non-root)模式。一般来说,只有虚拟控制软件(被成为是Virtual Machine Monitor,VMM)工作在根模式。

Intel官方曾表示,Intel虚拟技术需要一个该技术的处理器、芯片组、BIOS和VMM(Virtual Machine Monitor )的支持,其实际性能很大程度上取决于硬件和软件的配置。对于第三方主板商来说,要支持Intel虚拟技术,必须开发自己的支持Intel虚拟技术的BIOS。

在虚拟技术方面,Intel与AMD再次对峙。虽依据的原理相同,但设计出的技术两家公司还是有差别的。在2005年3月2日的IDF上,Intel公司和AMD分别宣称,各自的硬件虚拟技术平台将会极大地推动创新。在大会上,Intel公司展出了其虚拟技术代号为“Vanderpool”,该技术将于今年在桌面芯片和64位安腾处理器中推出,2006年在至强服务器芯片和移动处理器中推出。AMD也将于本月推出代号为“Pacifica”的虚拟技术,该技术将于2006年中期应用于AMD64位处理器中。Pacifica技术最突出的地方在于对内存控制器的改进方面。“Pacifica”通过Direct Connect Architecture(直接互连架构)和在CPU和内存控制器中引入一个新模型和功能来提高CPU的虚拟应用。

虚拟技术的前景是非常光明的。从硬件层面讲,虚拟技术对操作系统作用非常巨大,它使用户在单个服务器或是虚拟平台上运行多个操作系统,使IT资源管理更加方便灵活。在推进虚拟技术的进程中,Intel公司和AMD都得到了微软和VMware公司的支持。刘易斯(AMD商务软件战略师)称:她预测会有更多的软件制造商开发虚拟技术,这些技术将能在芯片制造商的平台上运行,这将会推动这项技术在用户中的普及。

不同的操作系统能够以最高的性能运行单独的任务,而各个任务之间彼此互不干扰。Intel公司和AMD却希望将这一技术移植到x86架构计算机系统上,它们认为,不仅仅是低端服务器,就连个人计算机也需要这种功能。据Intel公司数字办公室规划和营销部门的主管格雷戈里布赖恩特在上周IDF期间的一次研讨会上表示,例如,PC可以被划分为不同的部分,分别用于处理企业任务、个人任务和系统管理员对系统进行更新;家用计算机可以在一个分区上录制数字视频,而在其它分区上完成正常的任务。只要使用EMC的VMware或微软的Virtual Server等软件,在x86计算机的不同分区上运行多种操作系统是完全可能的。

尽管这项技术在IDF大会上引起了不小的反应,但其仍存在许多问题,其中包括如何和微软和VMware公司软件融合等问题。

Vanderpool和Pacifica是否兼容?现在还不好说,但这是个很严重的问题。当初AMD暗示Pacifica可能不兼容Intel的技术时,Illuminata公司的分析师乔纳森尤妮斯表示,AMD会愚蠢到推出一种与Vanderpool不兼容的虚拟技术是很难想象和理解的,这会使许多软件开发商感到痛心。AMD和Intel公司之间的大多数x86指令集是相同的,这意味着Windows、Photoshop等软件可以运行在两家公司的处理器上。但不同的指令集就会带来问题,像AMD和Intel公司分别在x86处理器上增添了64位计算技术,微软公司已经明确表示,它只会支持一种技术。

虚拟技术的效用问题也很另人关注,Illuminata公司的分析师高登胡佛(Gordon Haff)称,“问题是,这种技术究竟能在多大程序上提高产品性能,目前我们尚无法回答。VMware公司称效果并不好,但我们不知道。”他提醒用户,不要指望通过采用虚拟化的芯片就可以创建虚拟设备,“你还要在软件上进行投资。”

3、片上系统时代SoC

在ATI新的图形核心X1000中,由于内建H.264硬件解码技术,从而使得CPU从繁重的解码工作中解放出来。这是一个很好的设计,如果大家留意身边的硬件产品,类似的设计相当多。特别是当芯片电路设计逐步完善的今天,将一项特殊处理功能植入硬件已不是什么难事。

Intel的科学家认为,未来处理器将朝着类似片上系统的方向发展,CPU除了包括1个通用处理器外,还将包括TCP/IP卸载引擎(TCP/IP Offload Engine,简称TOE)、MPEG编码解码引擎、图形处理引擎。这些专用处理电路提供更高的处理效率的同时,还可以减少功耗和散热问题,推动摩尔定律继续向前发展。

IBM的科学家提出了类似观点,认为未来的处理器将集成目前操作系统的很多底层功能,提高操作系统的运行效率。相应地,操作系统、虚拟机、开发语言和工具将执行更高层次的功能,底层功能由硬件实现来提高运行速度和可靠性。

这种发展趋势不是IT公司自己的臆想,而是技术发展的必然。为了满足未来万兆以太网络的需求,处理器必须每67ns时间处理一个IP数据包,这样的任务超越了通用处理器结合操作系统的运算技术所能达到的极限。2003年11月,Intel公布了一款内部代号为TIPP的90nm专用处理器,包含46万个晶体管,能以高达9.64Gbps的实测数据率进行TCP/IP输入处理。这款处理器是使用软件可编程方法来进行TCP/IP卸载处理研究活动的一部分。该处理器核心引擎整合到片上系统(SoC)中,可以在万兆以太网卡上实现TCP/IP卸载(TCP/IP Offload),也可以成为未来中央处理器的一部分。

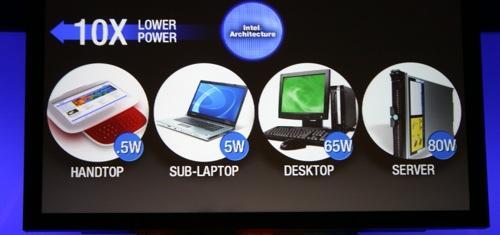

CPU发展的另外一个趋势也值得关注,那就是CPU厂商加大对嵌入式处理器的投入。威盛公司CPU产品市场部吴亿盼认为:“X86结构兼容性、延伸性比较好,其所提供的处理器平台与多样化的芯片组可以结合起来,为客户提供丰富的选择。”

AMD希望把 x86架构打造成无所不在的平台,使得x86架构可以延伸到所有的应用,包括从最高端性能的服务器到低功耗的掌上电脑。威盛则希望把X86处理器扩展到家庭商业娱乐、商业办公、物流、汽车、游戏机、瘦客户机等应用。

CPU正在这样飞速前进同时又不失规则地发展。摩尔定律只是CPU发展的一个航标,仅此而已。它在导航的同时也被一次次冲击着,但又由于一项项新产品新技术的提出,维护着它神话般的王者地位。

市场有需求,速度要前进,在实际应用的要求下,CPU不断成长。先进的制造技术,加上优秀的核心设计,这就是CPU的发展之路。其实CPU的发展也有“粗犷型”和“集约型”,只重视生产工艺的提升,不断加入晶体管就是“粗犷型”发展,而“好的架构设计 先进的生产工艺”就是我们所提倡的“集约型”发展。同时还有一个很重要的问题就是平衡性设计,一款CPU既不能过度依赖新工艺,也不能只靠架构打天下。要看到的是,Pentium 4在艰难发展的同时,为Intel成熟了多项生产工艺。这些都将给Intel下一代CPU发展铺平道路,所以Intel有信心制造新一代绝对低功耗的CPU,这也造就了Intel最大的一次路线转变。

参考文献:

从CPU的发展看五大半导体厂商技术对比 博客中国

看清Intel下一代处理器架构 微型计算机 阿汤

摩尔定律 不惑之年 计算机世界网 丁伟

新一代存储器编译器续写摩尔定律神话 电子工程专辑

- 吹尽黄沙始见金,历述CPU架构与工艺

- 吹尽黄沙始见金,历述CPU架构与工艺

- 吹尽黄沙始得金——华章4月图书推荐

- 黄沙落尽便是花

- 吸塑与吹塑工艺介绍

- CPU 工艺与发热量关系

- 浅谈关于CPU的架构和工艺(1)

- 转贴:cpu制作工艺

- CPU制作工艺中的14nm工艺

- 简谈BOM与工艺

- 黄沙遍地

- CPU制造工艺完整过程(图文)

- 手机CPU知识扫盲:谈谈手机CPU架构与原理

- ARM与X86 CPU架构对比区别

- ARM与X86 CPU架构对比区别

- ARM与X86 CPU架构对比区别

- ARM与X86 CPU架构对比区别

- CPU内部架构与工作原理

- 关于IFRMAE访问引用页面的元素

- 页面自动刷新或跳转--说明

- BIOS的磁盘读取

- MSDN的快捷方式

- C语言字节对齐详解

- 吹尽黄沙始见金,历述CPU架构与工艺

- c# 动态改变panel大小的问题

- EDA(VHDL)数字钟

- Adobe Flash CS4简体中文正式版下载

- VirtualBox安装

- 【其他】【RQNOJ】奇怪的电梯

- Linux命令记录

- sizeof

- 推荐发博客的工具:ScribeFire