[转]同步复位和异步复位

来源:互联网 发布:淘宝联盟pid在哪里看的 编辑:程序博客网 时间:2024/04/29 12:27

推荐的复位方式:异步复位、同步释放

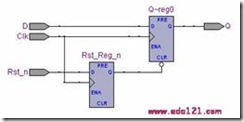

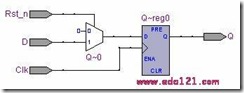

描述代码及对应的RTL电路:

HDL源代码

对应的RTL电路

module Rst_Circuit( Rst_n, Clk, D, Q ); input Rst_n; input Clk; input D; output Q; reg Rst_Reg_n; reg Q; always @(posedge Clk) begin //将异步复位信号先用Clk同步一下

Rst_Reg_n <= Rst_n; end //如果没有加"or negedge Rst_Reg_n",将变成同步复位

always @(posedge Clk or negedge Rst_Reg_n) begin if (~Rst_Reg_n) begin Q <= 1'd0; end else begin Q <= D; end end endmodule

注:最好在模块外面将异步复位信号同步好,再送至各模块,这样各个模块内部就不需要再分别单独同步了。

下面具体阐述一下同步、异步复位的区别,以及为什么要采用这种方式的原因。

复位电路是每个数字逻辑电路中最重要的组成部分之一。

复位电路有两个工作目的:

1、 仿真的时候使电路进入初始状态或者其它预知状态;

2、 对于综合实现的真实电路,通过复位使电路进入初始状态或者其它预知状态。

一般来说,逻辑电路的任何一个寄存器、存储器结构和其它逻辑单元都必须要附加复位逻辑电路,以保证电路能够从错误状态中恢复,可靠地工作。

常用的复位信号为低电平有效信号,在应用时外部引脚接上上拉电阻,这样能增加复位电路的抗干扰性能。

复位方式大致分为两类,即同步复位和异步复位。这两种复位方式各有优缺点,其应用场合也各不相同。

同步复位

异步复位

所谓同步复位是指当复位信号发生变化时,并不立刻生效,只有当有效时钟沿采样到已变化的复位信号后,才对所有寄存器复位。同步复位的应用要点如下:

· 指定同步复位时,always的敏感表中仅有时钟沿信号,仅仅当时钟沿采到同步复位的有效电平时,才会在时钟沿到达时刻进行复位操作。

所谓异步复位是指当复位信号有效沿到达时,无论时钟沿是否有效,都会立即对目标(如寄存器、RAM等)复位。异步复位的应用要点如下:

· 指定异步复位时,只需always的敏感表中加入复位信号的有效沿即可,当复位信号有效沿到达时,无论时钟沿是否有效,复位都会立即发挥其功能。

module Rst_Circuit( Rst_n, Clk, D, Q ); input Rst_n; input Clk; input D; output Q; reg Q; always @(posedge Clk) //同步复位 begin if (~Rst_n) begin Q <= 1'd0; end else begin Q <= D; end end endmodule module Rst_Circuit( Rst_n, Clk, D, Q ); input Rst_n; input Clk; input D; output Q; reg Q; //如果没有写"or negedge Rst_n",将变成同步复位

always @(posedge Clk or negedge Rst_n) begin if (~Rst_n) begin Q <= 1'd0; end else begin Q <= D; end end endmodule · 如果目标器件或可用库中的触发器本身包含同步复位端口,则在实现同步复位电路时可以直接调用同步复位端。然后很多目标器件(如PLD)和ASIC 库的触发器本身并不包含同步复位端口,这样复位信号与输入信号组成某种组合逻辑(比如复位低电平有效,只需复位与输入信号相与即可),然后将其输入到寄存 器的输入端。为了提高复位电路的优先级,一般在电路描述时使用带有优先级的if...else结构,复位电路在第一个if下描述,其它电路在else或else...if分支中描述。

· 大多数目标器件(如FPGA和CPLD)和ASIC库的触发器都包含异步复位端口,异步复位会被直接接到触发器的异步复位端口,如图所示:

同步复位的优点如下:

· 同步复位利于基于周期机制的仿真器进行仿真;

· 使用同步复位可以设计100%的同步时序电路,有利于时序分析,其综合结果的频率往往较高;

· 同步复位仅在时钟的有效沿生效,可以有效地避免因复位电路毛刺造成的亚稳态和错误。同步复位在进行复位和释放复位信号时,都是仅当时钟 沿采到复位信号电平变化时才进行相关操作,如果复位信号树的组合逻辑出现了某种毛刺,此时时钟沿采样到毛刺的概率非常低,这样通过时钟沿采样,可以十分有 效地过滤复位电路组合逻辑产生的毛刺,增强了电路稳定性。

异步复位的优点如下:

· 由于多数目标器件(如FPGA和CPLD)和ASIC库的触发器都包含异步复位端口,异步复位会节约逻辑资源;

· 异步复位设计简单;

· 对于大多数FPGA,都有专用的全局异步复位/置位资源(GSR,Global Set Reset),使用GSR资源,异步复位到达所有寄存器的偏斜(skew)最小。

同步复位的缺点如下:

· 很多目标器件(如FPGA和CPLD)和ASIC库的触发器本身并不包含同步复位端口,使用同步复位会增加更多逻辑资源;

· 同步复位的最大问题在于必须保证复位信号的有效时间足够 长,这样才能保证所有触发器都能有效地复位。由于同步复位仅当时钟沿采样到复位信号时才会进行复位操作,所以其信号的持续时间起码要大于设计的最长时钟周 期,以保证所有时钟的有效沿都能采样到同步复位信号。事实上,仅仅保证同步复位信号的持续时间大于最慢的时钟周期还是不够的,设计中还要考虑到同步复位信 号树通过所有相关组合逻辑路径时的延时,以及由于时钟布线产生的偏斜(skew)。这样,只有同步复位大于时钟最大周期,加上同步信号穿过的组合逻辑路径 延时,再加上时钟偏斜延时,才能保证同步复位可靠、彻底。如图所示,假设同步复位逻辑树组合逻辑的延时为t1,复位信号传播路径的最大延时为t2,最慢时 钟的周期为Period_max,时钟的skew为Clk2-Clk1,则同步复位的周期Tsyn_rst应该满足如下公式:

Tsyn_rst > Period_max + (Clk2 – Clk1) + t1 + t2

异步复位的缺点如下:

· 异步复位的作用和释放与时钟沿没有直接关系,异步复位生效时问题并不明显;但是当释放异步复位时,如果异步复位信号释放时间和时钟的有效沿到达时间几乎一致,则容易造成触发器输出为亚稳态,形成逻辑错误;

· 如果异步复位逻辑树的组合逻辑产生了毛刺,则毛刺的有效沿会使触发器误复位,造成逻辑错误。

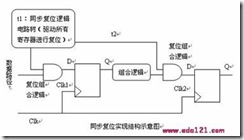

推荐的复位电路设计方式是异步复位、同步释放。这种方式,可以有效地继承异步复位设计简单的优势,并克服异步复位的上述风险和缺陷。在FPGA和CPLD等可编程逻辑器件设计中,使用异步复位、同步释放可以节约器件资源,并获得稳定可靠的复位效果。

reg Rst_Reg_n; reg Q; always @(posedge Clk) beginRst_Reg_n <= Rst_n; //将异步复位信号先用Clk同步一下

end always @(posedge Clk or negedge Rst_Reg_n) //如果没有写"or negedge Rst_Reg_n",将变成同步复位

begin if (~Rst_Reg_n) begin Q <= 1'd0; end else begin Q <= D; end end这里使用时钟将外部输入的异步复位信号寄存一个节拍后,再送到触发器异步复位端口的设计方法的另一个好处在于,做STA(静态时序分析)分析时,时序工具会自动检查同步后的异步复位信号和时钟的到达(Recovery)/撤销(Removal)时间关系,如果因布线造成的skew导致该到达/撤销时间不能满足,STA工具会上报该路径,帮助设计者进一步分析问题,如图所示:

- [转]同步复位和异步复位

- 同步复位和异步复位

- 异步复位和同步复位

- [转]同步复位,异步复位以及异步复位同步释放

- 同步复位和异步复位的比较

- 同步复位和异步复位的比较

- 异步复位和同步复位的区别

- 同步复位和异步复位的比较

- FPGA中异步复位和同步复位

- verilog同步复位和异步复位

- 同步复位和异步复位的对比

- 同步复位和异步复位的比较

- Verilog同步复位,异步复位

- 同步复位与异步复位

- [转]异步复位、同步释放

- 异步复位、同步复位和异步复位同步释放的比较

- 【Verilog】 同步复位和异步复位比较 async vs. sync

- 同步复位和异步复位的比较(转载)

- 线程池

- 使用string,ostringstream等需要注意的事

- 平面切分空间

- PCWorld:谷歌成下一个微软式企业10大理由

- 【转】讲解安装Ubuntu nfs配置系统

- [转]同步复位和异步复位

- Android 体系架构

- ubuntu中samba服务器的简单配置方法

- linux 下libpcap和windows下winpcap 捕获网络数据包的异同

- Android中采用的MVC框架

- 2378

- 基于TMS320DM355的VGA视频采集系统的设计与实现

- 详细分析Ndis协议驱动和Ndis中间层过滤驱动区别(Ndisprot和passthru)

- android开发中JAVA调用C++