【连载】【FPGA黑金开发板】Verilog HDL那些事儿--GUI系统(二十五)(大结局)

来源:互联网 发布:阿里云1m带宽日访问量 编辑:程序博客网 时间:2024/04/27 15:40

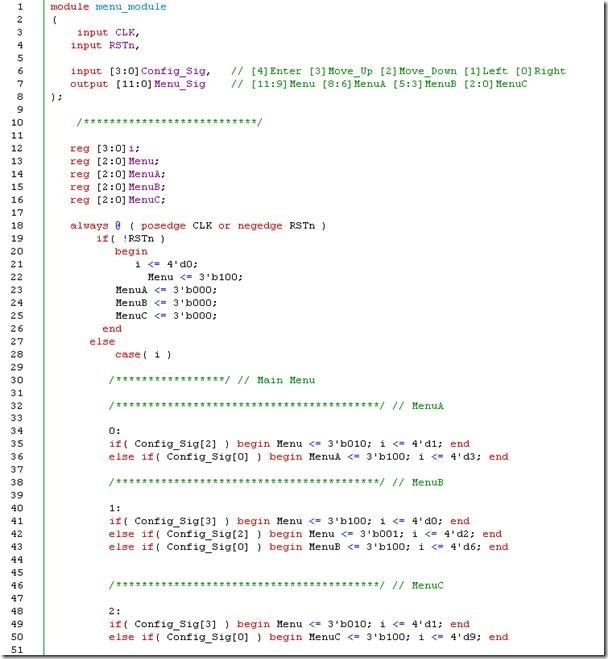

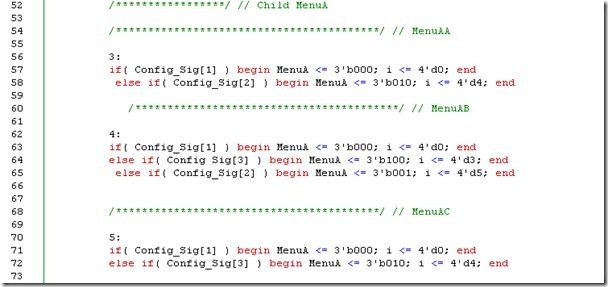

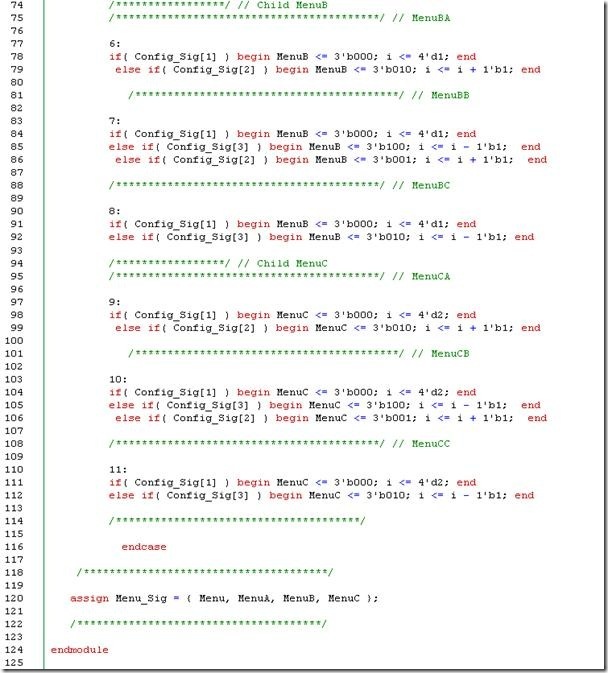

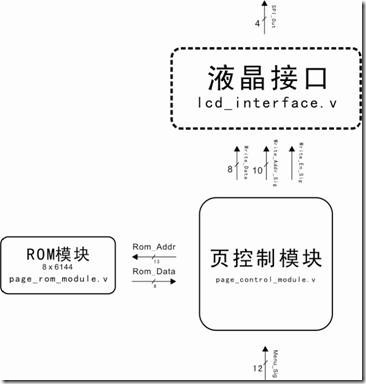

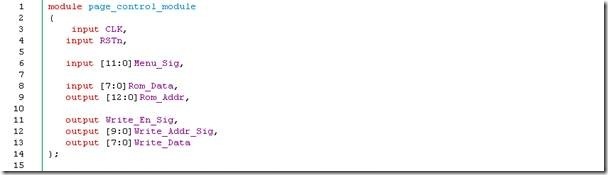

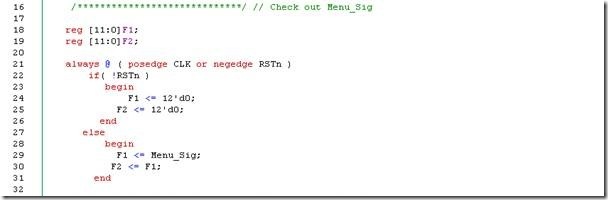

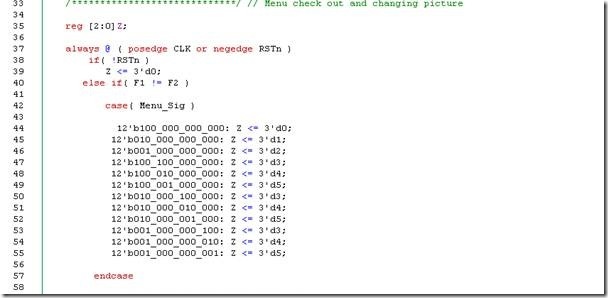

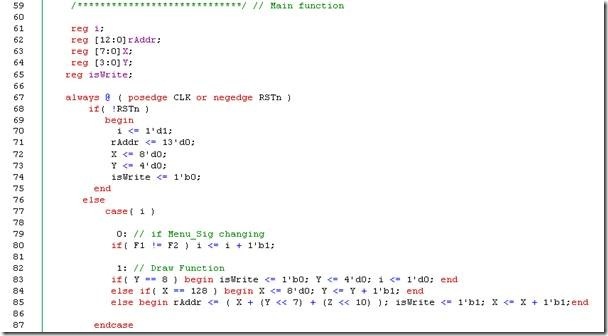

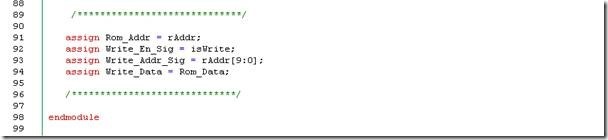

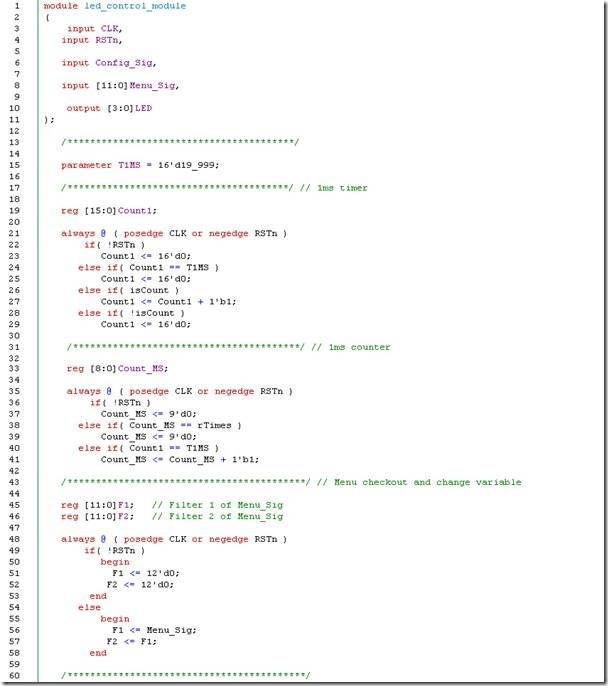

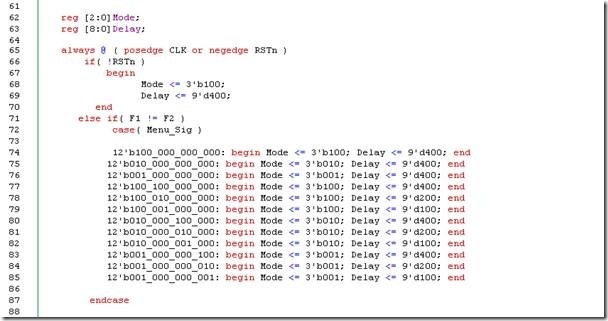

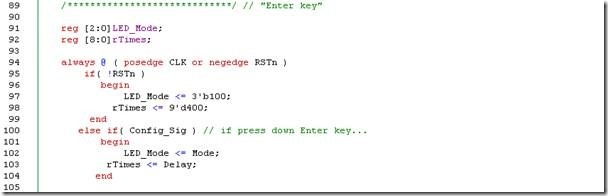

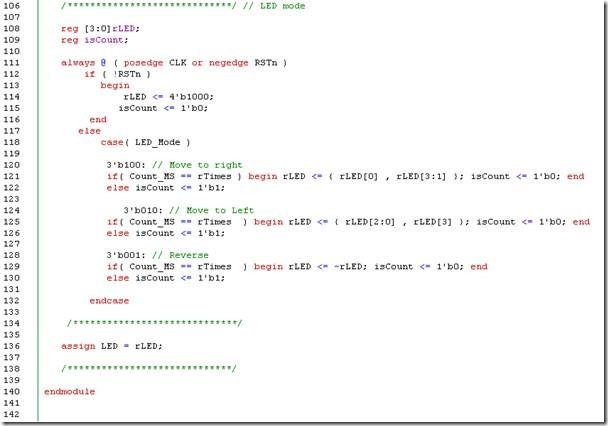

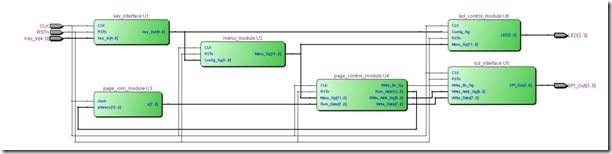

终于写到这本笔记的尾声了,在6.1章和6.2章,笔者所建立的系统都是由几个接口东拼西凑组合而成,那并非“系统建模”的主要意义,而是一个概念而已。在这一章笔者用另一种概念,一种更接近“系统建模”的实例。同时间我们也探讨“接口”对“系统建模”的重要性。 上图是“GUI系统”的层次关系。Menu代表主目录,MenuA,MenuB 和 MenuC 代表子目录。然而每一个目录的图像都有代表的意义: 向右的流水灯效果 延迟400ms 向左的流水灯效果 延迟200ms 闪耀效果 延迟100ms “GUI系统”有一个经典的难题就是“目录指针”。当我们从什么目录,什么选项切换到什么目录,什么选项,该“目录指针”都要一一追踪。想到“指针”读者一定会联想到C语言的“变量指针”,“函数指针”和“结构体指针”等。 reg [2:0]Menu; // 建立一个寄存器表示该目录Flag Menu[2] = 选项A的Flag // 向右的流水灯效果的选项 Menu[1] = 选线B的Flag // 向左的流水灯效果的选项 Menu[0] = 选线C的Flag // 闪耀效果的选项 假设,默认的选项是“向右的流水灯效果”,那么Menu寄存器经初始化过后的赋值是 3'b100。再假设,我从当前的“向右的流水灯效果”向下切换至“向左的流水灯效果” Menu寄存器的值表示 2'b010; 同样的道理,我们可以为每一个Menu选线的子目录创建一个子“目录Flag”: reg [2:0]MenuA; // MenuA 的目录Flag reg [2:0]MenuB; // MenuB 的目录Flag reg [2:0]MenuC; // MenuC 的目录Flag MenuA[2] = 选项A的Flag // 向右流水灯效果的“400ms延迟”选项 MenuA[1] = 选线B的Flag // 向右流水灯效果的“200ms延迟”选项 MenuA[0] = 选线C的Flag // 向右流水灯效果的“100ms延迟”选项 MenuB[2] = 选项A的Flag // 向左流水灯效果的“400ms延迟”选项 MenuB[1] = 选线B的Flag // 向左流水灯效果的“200ms延迟”选项 MenuB[0] = 选线C的Flag // 向左流水灯效果的“100ms延迟”选项 MenuC[2] = 选项A的Flag // 闪耀效果的“400ms延迟”选项 MenuC[1] = 选线B的Flag // 闪耀效果的“200ms延迟”选项 MenuC[0] = 选线C的Flag // 闪耀效果的“100ms延迟”选项 output [11:0]Menu_Sig; assign Menu_Sig = { Menu, MenuA, MenuB, MenuC }; Menu_Sig[11..0] { Menu, MenuA, MenuB, MenuC } 选项 12'b100_000_000_000 向右的流水灯效果的选项 12'b010_000_000_000 向左的流水灯效果的选项 12'b001_000_000_000 闪耀效果的选项 12'b100_100_000_000 向右的流水灯效果“延迟400ms”的选项 12'b100_010_000_000 向右的流水灯效果“延迟200ms”的选项 12'b100_001_000_000 向右的流水灯效果“延迟100ms”的选项 12'b010_000_100_000 向左的流水灯效果“延迟400ms”的选项 12'b010_000_010_000 向左的流水灯效果“延迟200ms”的选项 12'b010_000_001_000 向左的流水灯效果“延迟100ms”的选项 12'b001_000_000_100 闪耀效果“延迟400ms”的选项 12'b001_000_000_010 闪耀效果“延迟200ms”的选项 12'b001_000_000_001 闪耀效果“延迟100ms”的选项 12'b100_100_000_000 这样的设计有一个好处,就是“方便理解”。 Config_Sig[4..0] 分配 功能 Config_Sig[4] Enter (保留) Config_Sig[3] 上 Config_Sig[2] 下 Config_Sig[1] 左 Config_Sig[0] 右 Config_Sig[4] 被保留作为其他用途。 (一)Config_Sig[2] 接收一个高脉冲,从“向右流水灯效果”选项,向下切换至“向 左流水灯效果”选项。 (二)Config_Sig[0] 接收一个高脉冲,就会切入“向右流水灯效果”的子目录选项。 笔者再假设一个情况,如果“向右流水灯效果”的“400ms延迟”作为开始选项,那么: (一)Config_Sig[2] 接收一个高脉冲,从“向右流水灯效果”的“400ms延迟”选 项,向下切换至“向右流水灯效果”的“200ms延迟”选项。 (二)Config_Sig[1] 接收一个高脉冲,从“向右流水灯效果”的“400ms延迟”选 项(子目录)退回从“向右流水灯效果”选项(目录)。 至于目录从哪里来又切换至那里去,读者就浏览“GUI系统的目录”吧。 menu_module.v 主要的功能就是跟踪“目录路径”而已。也就是说“GUI系统”的“目录路径”会因为Config_Sig 信号而产生变化,然而这个模块只是跟踪,然后更改 Menu_Sig。具体的功能还是直接看代码比较强。 在12~16行是核心功能中所使用的寄存器。Menu是主目录Flag的寄存器,MenuA是Menu 的A项的子目录Flag寄存器,其他的 MenuB 和 MenuC 都是大同小异。在这里有一点必须注意,在“GUI系统”初始化的时候Menu的A项作为默认选项,所以在21~25行Menu寄存器的值初始化为 3'b100。 30~50行就是主目录Menu,根据Config_Sig信号产生的结果。初头会进入步骤0,亦即主目录Menu的A项,在35行是向下切换的动作(Menu寄存器赋值为3'b010,进入步骤1),36行是切入子目录的动作(Menu寄存器清理,MenuA寄存器赋值3'b100,进入步骤3),亦即进入子目录后,子目录的A项作为默认。步骤1和2分别是 Menu的B项和C项。主目录Menu项与项之间的切换都根据“GUI系统”的“目录结构”。 上图是“GUI系统”的全图形(不要被吓到),笔者会慢慢解释的。 “目录模块”就如前面说所那样,它是跟踪“GUI系统”的“目录路径”,该模块只需要Config_Sig[3..0],然而随着Config_Sig[3..0]的配置,输出信号Menu_Sig,也会随着更改。 上面的“图形”和实验二十演示(LCD接口演示实验)非常相似吧。ROM模块所拥有的空间是 8 Bits x 6144 Words,亦即这个ROM模块储存了 6 x 8 Bits x 1024 Words,也就说它包含了6副 8 Bits x 1024 Words 的图像信息。 地址0~1023 是“向右流水灯效果”的图像信息。 地址1024~2047 是“向左流水灯效果”的图像信息。 地址2048~3071 是“闪耀效果”的图像信息。 地址3072~4095 是“400ms延迟”的图像信息。 地址4096~5119 是“200ms延迟”的图像信息。 地址5120~6143 是“100ms延迟”的图像信息。 page_control_module.v 的输入输出接口。 16~32行这一行代码和detect_module.v 很相识,但是我们不是要检测电平的变化,而是要检测“Menu_Sig”的变化。当Menu_Sig 产生变化的时候 上一个时间的Menu_Sig 和 下一个时间的Menu_Sig 的值是不一样,然而F1寄存器暂存下一个时间的Menu_Sig ,F2寄存器则暂存 上一个时间的 Menu_Sig。 当我们要检测 Menu_Sig 是否发生变化的时候,可以这样表达: if( F1 != F2 ) // Menu_Sig 发生变化 ...... // 执行语句 else // Menu_Sig 没有发生变化 ...... // 执行语句 Z值 图像信息 Z值 图像信息 0 “向右流水灯效果”图像信息 3 “延迟400ms”图像信息 1 “向左流水灯效果”图像信息 4 “延迟200ms”图像信息 2 “闪耀效果”图像信息 5 “延迟100ms”图像信息 在 40行表示了“当Menu_Sig产生变化,就根据Menu_Sig的值,更新Z寄存器的值”。 左图是LED控制模块的图形,该控制模块会根据不同的Menu_Sig 产生不同的LED效果。然而该控制模块不会像 page_control_module.v 那样,在Menu_Sig产生变化的瞬间,输出也会产生变化。每当Menu_Sig 产生变化,如果Config_Sig[4] 没有接收一个高脉冲,是LED的输出效果是不会更新的。Config_Sig[4]在位分配的意义上正是“Enter”的效果。 第15是1ms的常量定义。在19~29行是1ms的定时器。33~41行是1ms的计数器。 45~58行是用来暂存上一个时间的Menu_Sig 和下一个时间的Menu_Sig,和page_control_module 的16~31行是同样的道理。 3'b010 表示向左流水灯效果,3'b001表示闪耀效果。 整个“GUI系统”就是 menu_module.v , page_control_module.v 和 lcd_interface.v 。该“GUI系统”在“显示”方面的设计比较简单,就是“一个事件一副图像”。此外“什么事件,产生什么效果”,这就是不主要了。 “接口在系统建模中扮演的角色”此外还有“系统不同的概念”。 笔记终于写到这里,从第一章开始到第五章,所有的实验,所有的内容都是在为第六章作基础。 “什么是系统”这个问题其实笔者也是考过许多,但是“系统”这东西涉及的东西实在是太多了,由此笔者又延伸几个问题出来“什么是系统建模?”,“系统建模应该作什么?”实验二十二和二十三就是用来回答“什么是系统建模”,实验二十四则是用来回答“系统建模应该做什么”。 “系统建模”比起“基础建模”或者“封装(接口建模)”不是同一个等次的东西。因为“系统建模”的建模量不是一般的多,而是非常多。如果没有建模技巧,要完成“系统建模”是一件苦差事。 “系统建模”作为“低级建模”结束的一页,是再适合不过了。就如笔者在前面说所的,“前期的建模是为后期的建模作准备”。显然“系统建模”不可能是后期建模的最后一站,在“系统建模”的后面还有更后期的建模。但是那是什么,笔者也不知道甚么... 笔者只知道一个事实“当读者有本事走到这里,完成·明白什么是系统建模,读者就已经了解什么是低级建模”。在笔者的眼里“系统建模”是“低级建模”的综合练习,因为要清楚的表达“系统建模的结构”,读者必须掌握好“低级建模”的所有基础。无论是“代码风格”,“模块性质”,“建模结构”等,少了一样也不行。 读者呀: 是不是更上一层的明白“低级建模”的基本概念呢?一个大东西是需要许多的小东西不停的组成和不停的组合。在组合的过程要相互尊重(明白模块之间的性质),相互协调(不同性质的模块之间的调用),相互支持(一层接一层的组合)... 终于把这本笔记编辑完毕了,编辑笔记的过程真是辛酸但是又是真实。编写这本笔记的锄头笔者是重新从零开始的。说实话,笔者在编辑这本笔记之前水平很低,但是当笔者掌握了“建模技巧”之后,跳跃式的进步。读者们相不相信,就见仁见智。 话说3个月的时间说长不长说短不短,悄悄好是四份之一年,但是这一段时间对于笔者来说是绝对真实而且值得的。当这本笔记完成之际,笔者仿佛又多了解了 Verilog HDL+ FPGA的世界。Verilog HDL + FPGA的世界是深不可测,如果以笔者的话来说,笔者也仅是了解到冰山一角而已。但是这一步的踏出,笔者发现了新大陆。 好了,笔者不再罗嗦了。笔者真心的希望读者们可以借与这本笔记重新去认识 Verilog HDL + FPGA 的世界。Verilog HDL + FPGA 的世界一点也不可怕,而且多姿多彩,只是我们在学习的路上,忽然间迷失而已,只要重新思考,重新出发,就会发现这个世界的不同。 可能读者们产生这样的问题:“下一站的学习旅程,我应该选择哪里?”。笔者不能断定什么,但是笔者建议一下的几个选择: 一、了解功能仿真和验证(你会了解系统级的硬件描述语言)。 二、了解时序分析(你会了解寄存器级的世界)。 三、了解NIOS II(你会了解软核)。 四、继续走 Verilog HDL 的道路。 笔者的选择是第四点,因为笔者从这本笔记了解到 Verilog HDL 语言是很强大。笔者想更了解它 ...... 声明:本文转载于http://www.cnblogs.com/kingst,版权归akuei2及黑金动力社区(http://www.heijin.org)共同所有。

6.3 实验二十四:GUI系统

![clip_image002[9] clip_image002[9]](http://images.cnblogs.com/cnblogs_com/kingst/WindowsLiveWriter/FPGAVerilogHDLGUI_129A7/clip_image002%5B9%5D_thumb.jpg)

和5.8章一样 Config_Sig 中的每一位都对“高脉冲敏感”。menu_module.v

步骤1(40行),如果41行成立的话,就会切换回Menu的A项(Menu寄存器赋值为3'b100, 返回步骤0)。如果42行成立,就会切换到Menu的C项(Menu寄存器赋值为,3'b001,进入步骤2)。如果43行成立,就会切入Menu的B项的子目录(MenuB寄存赋值为3'b100, 进入步骤6)亦即进入子目录后,子目录的A项作为默认。

![clip_image002[12] clip_image002[12]](http://images.cnblogs.com/cnblogs_com/kingst/WindowsLiveWriter/FPGAVerilogHDLGUI_129A7/clip_image002%5B12%5D_thumb.jpg)

page_control_module.v

led_control_module.v

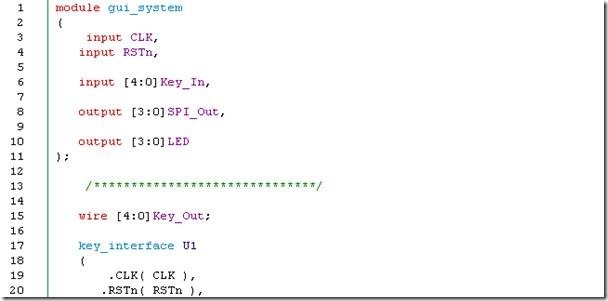

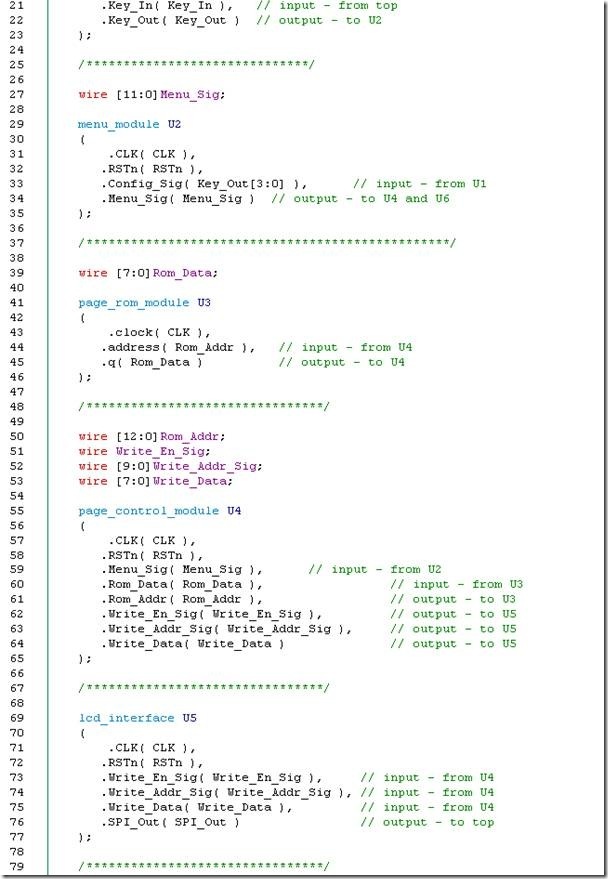

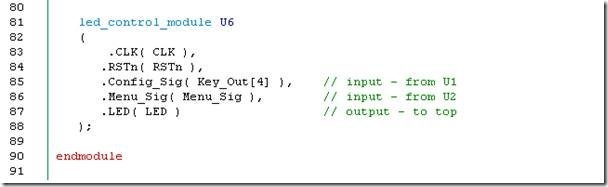

gui_system.v

实验二十四说明:

实验二十四结论:

总结:

结束语

- 【连载】【FPGA黑金开发板】Verilog HDL那些事儿--GUI系统(二十五)(大结局)

- 【连载】【FPGA黑金开发板】Verilog HDL那些事儿--系统建模(二十三)

- 【连载】【FPGA黑金开发板】Verilog HDL那些事儿--RTC系统(二十四)

- 【连载】【FPGA黑金开发板】Verilog HDL那些事儿--低级建模的基础(二)

- 【连载】【FPGA黑金开发板】Verilog HDL那些事儿--LCD(12864)封装(二十一)

- 【连载】【FPGA黑金开发板】Verilog HDL那些事儿--我眼中的FPGA 和Verilog HDL(一)

- 【连载】【FPGA黑金开发板】Verilog HDL那些事儿--独立按键封装(十五)

- 【连载】【FPGA黑金开发板】Verilog HDL那些事儿--12864(ST7565P)液晶驱动(十三)

- 【连载】【FPGA黑金开发板】Verilog HDL那些事儿--不是“编程”是“建模”(四)

- 【连载】【FPGA黑金开发板】Verilog HDL那些事儿--听听低级建模的故事(五)

- 【连载】【FPGA黑金开发板】Verilog HDL那些事儿--低级建模的资源(六)

- 【连载】【FPGA黑金开发板】Verilog HDL那些事儿--低级建模的基础实例(七)

- 【连载】【FPGA黑金开发板】Verilog HDL那些事儿--数码管电路驱动(八)

- 【连载】【FPGA黑金开发板】Verilog HDL那些事儿--PS2解码(九)

- 【连载】【FPGA黑金开发板】Verilog HDL那些事儿--VGA驱动(十)

- 【连载】【FPGA黑金开发板】Verilog HDL那些事儿--VGA驱动(十)

- 【连载】【FPGA黑金开发板】Verilog HDL那些事儿--串口模块(十一)

- 【连载】【FPGA黑金开发板】Verilog HDL那些事儿--串口模块(十一)

- [Android] Different between Padding and Margin in Layout

- 【连载】【FPGA黑金开发板】Verilog HDL那些事儿--RTC系统(二十四)

- 在CSDN建立自己的老巢--~_~

- 在word里面插入带对勾的框框

- RECT 结构

- 【连载】【FPGA黑金开发板】Verilog HDL那些事儿--GUI系统(二十五)(大结局)

- c++设计模式(1)-Singleton

- Git的基础

- ACM-宏定义常量的运行速度与常量的运行速度

- 六维空间PT下载站

- 确认信息框:Ext.MessageBox.confirm()

- C#获取程序路径的方法

- javaScript获取窗口的高度和宽度

- (linux)vi编辑器没有彩色显示解决