DSP28_Ev.h头文件说明(一)

来源:互联网 发布:通信设备软件研发 编辑:程序博客网 时间:2024/05/01 00:50

DSP28_Ev.h头文件较长,文章中不再贴出,需要网友的可以在网上整套下载。

TMS320F2812具有两个事件管理器模块EVA和EVB,每个EV模块都具有2个通用定时器、3个比较单元、3个捕获单元以及1个正交编码电路,这两个模块与电机控制密切相关,PWM输出,正交解码,比较,脉冲捕获等都可以通过它们实现。由于实现功能较多,与之配套的寄存器配置也比较复杂。

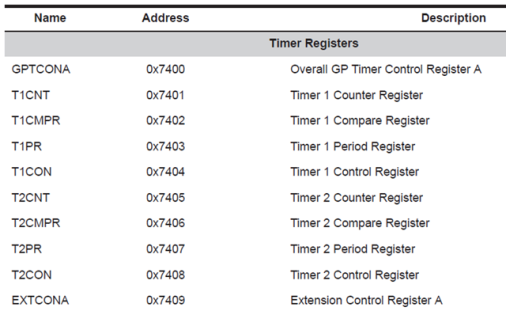

EVA的寄存器映射在0×7400~0×7431的区域,EVB的寄存器映射在0×7500~0×7531的区域,需要注意的是寄存器在地址的映射上是不连续的。由于EVA与EVB的功能相同,故以EVA作为代表,分析它的相关寄存器。

TMS320F2812的EV寄存器主要分为四类:Timer寄存器、Compare寄存器、Capture寄存器和Interrupt寄存器。

1. Timer寄存器

表1. EVA Timer寄存器映射地址表

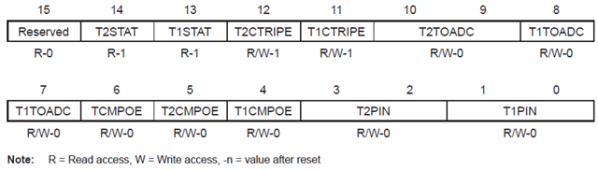

1.1. GPTCONA寄存器

0 递减计数

1 递增计数13T1STAT通用定时器1的状态位(只读)

0 递减计数

1 递增计数12T2CTRIPET2CTRIP使能位,使能/屏蔽定时器2比较输出(T2CTRIP)当EXTCON(0)=1,该位有效,EXTCON(0)=0,该位保留。

0 T2CTRIP屏蔽,T2CTRIP屏蔽不影响定时器2的比较输出、GPTCON(5)、PDPINT标志。

1 T2CTRIP使能,定时器2比较输出进入高阻态,GPTCON(5)设为0,PDPINT标志设为111T1CTRIPET1CTRIP使能位,使能/屏蔽定时器1比较输出(T1CTRIP)当EXTCON(0)=1,该位有效,EXTCON(0)=0,该位保留。

0 T1CTRIP屏蔽,T1CTRIP屏蔽不影响定时器2的比较输出、GPTCON(4)、PDPINT标志。

1 T2CTRIP使能,定时器2比较输出进入高阻态,GPTCON(4)设为0,PDPINT标志设为110-9T2TOADC定时器2时间启动ADC

00 定时器2事件不启动ADC

01 下溢中断启动ADC

10 周期中断启动ADC

11 比较中断启动ADC8-7T1TOADC定时器1时间启动ADC

00 定时器2事件不启动ADC

01 下溢中断启动ADC

10 周期中断启动ADC

11 比较中断启动ADC6TCMPOE定时器比较输出使能,使能/屏蔽定时器比较输出。当EXTCON(0)=0,该位有效,EXTCON(1)=1,该位保留。当TCMPOE有效,PDPINT/T1CTRIP为0,且EVIMRA(0)=1时,TCMPOE复位为0。

0 定时器比较输出T1/2PWM_T1/2CPM输出高阻

1 定时器比较输出T1/2PWM_T1/2CPM输出由各自定时器独立触发驱动5T2CMPOE定时器2比较输出使能,使能/屏蔽定时器2比较输出T2PWM

_T2CMP。当EXTCON(0)=1,该位有效,EXTCON(0)=0,该位保留。如果T2CTRIP被使能且为低电平,则T2CMPOE复位为低电平。

0 定时器2比较输出T2PWM_T2CPM输出高阻

1 定时器比较输出T2PWM_T2CPM输出由定时器2触发驱动4T1CMPOE定时器1比较输出使能,使能/屏蔽定时器1比较输出T1PWM

_T1CMP。当EXTCON(0)=1,该位有效,EXTCON(0)=0,该位保留。如果T1CTRIP被使能且为低电平,则T1CMPOE复位为低电平。

0 定时器1比较输出T1PWM_T1CPM输出高阻

1 定时器比较输出T1PWM_T1CPM输出由定时器1触发驱动3-2T2PIN通用定时器2比较输出极性

00 强制低

01 低有效

10 高有效

11 强制高1-0T1PIN通用定时器1比较输出极性

00 强制低

01 低有效

10 高有效

11 强制高

注:1). 当EXTCON[1]第一次设为1时,GPTCONA[11]和GPTCONA[12]的默认值为1;

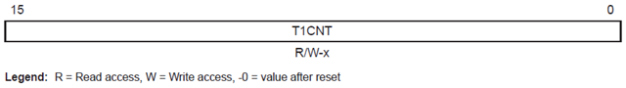

1.2. T1CNT寄存器

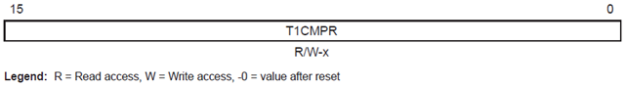

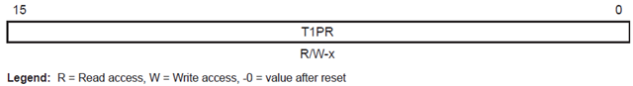

1.3. T1CMPR

1.4. T1PR

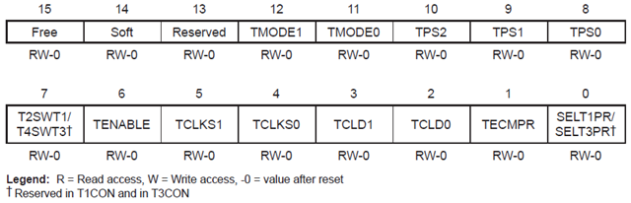

1.5. T1CON

00 仿真挂起时,立即停止

01 仿真挂起时,当前定时器周期完成后停止

10 仿真挂起不影响操作

11 仿真挂起不影响操作13RESERVED读为0,写无效12-11TMODE1-TMODE2计数模式选择

00 停止/保持

01 连续增/减计数模式

10 连续增计数模式

11 定向增/减计数模式10-8TPS2-TPS0输入时钟预分频器

000 x/1

001 x/2

010 x/4

011 x/8

100 x/16

101 x/32

110 x/64

111 x/128(HSPCLK)7T2SWT1T2SWT1是EVA的定时器控制位,它是使用定时器1启动定时器2的使能位,在T1CON中位保留位。

0 使用自己的使能位(TENABLE)

1 使用T1CON的使能位,忽略自己的使能位6TENABLE定时器使能位

0 定时器禁用,定时器被置为保持状态且预分频器复位

1 定时器使能5-4TCLKS(1,0)时钟源选择

00 内部时钟(例如,HSPCLK)

01 外部时钟(例如,TCLKINx)

10 保留位

11 QEP电路3-2TCLD(1,0)定时器比较寄存器装载条件

00 计数器值为0

01 计数器值为0或等于周期计数器值

10 立即装载

11 保留位1TECMPR定时器比较使能

0 禁用定时器比较操作

1 使能定时器比较操作0SELT1PRSELT1PR是EVA的定时器控制位,周期寄存器选择位。当T2CON等于1时,定时器1和定时器2都使用定时器1的周期寄存器。T1CON的该位为保留位。

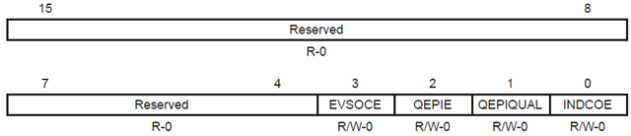

1.6. EXTCONA寄存器

0 禁止EVSOC‘输出,EVSOC’处于高阻态

1 使能EVSOC‘输出2QEPIEQEP索引使能位1QEPQUALCAP3_QEPI1索引确认模式0INDCOE比较输出的单独使能模式

注:EXTCONA寄存器,基本上不能理解其作用,看看随着学习的深入是不是可以学习到相关的知识.

- DSP28_Ev.h头文件说明(一)

- DSP28_Ev.h头文件说明(二)

- DSP28_Ev.h头文件说明(三)

- DSP28_Ev.h头文件说明(四)

- DSP28_Adc.h头文件说明(一)

- getopt.h 头文件说明

- linux/compile.h头文件说明

- linux/compile.h头文件说明

- DSP28_DevEmu.h头文件寄存器说明

- MFC之StdAfx.h头文件说明

- linux/compile.h头文件说明

- DSP28_Sci.h头文件说明1

- DSP28_Sci.h头文件说明2

- Android JNI .h头文件生成说明

- sys/param.h 和 limits.h头文件说明

- (一)ImageProcess软件学习--BmpFile.h头文件

- linux内核list.h头文件分析(一)

- jni.h头文件详解(一)

- DSP28_DevEmu.h头文件寄存器说明

- flash 工作原理

- DSP28_Adc.h头文件说明(一)

- 人生哲理

- SQL 获取服务器IP/客户端IP

- DSP28_Ev.h头文件说明(一)

- Latex文字大小设置

- SQL获得当前连接客户端IP和机器名

- MPlayer编解码开发指导

- Control Compile Output

- DSP28_Ev.h头文件说明(二)

- DSP28_Ev.h头文件说明(三)

- 内存模型2

- DSP28_Ev.h头文件说明(四)