第4章 ISE开发环境使用指南[FPGA开发实用教程]——第2节 HDL代码输入

来源:互联网 发布:xp禁止自动安装软件 编辑:程序博客网 时间:2024/06/06 05:22

4.2.1 新建工程

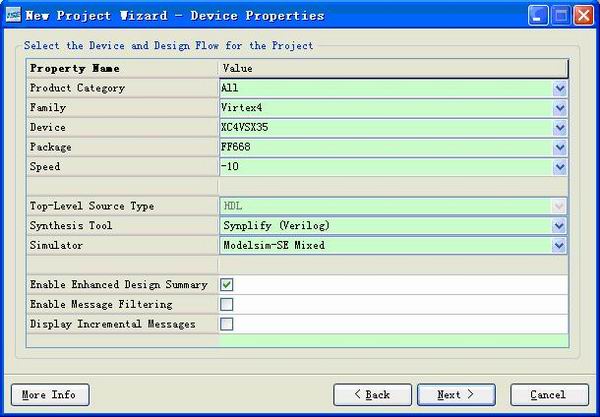

首先打开ISE,每次启动时ISE都会默认恢复到最近使用过的工程界面。当第一次使用时,由于此时还没有过去的工程记录,所以工程管理区显示空白。选择File|New Project选项,在弹出的新建工程对话框中的工程名称中输入“one2two”。在工程路径中单击Browse按键,当工程放到指定目录,如图4-7所示。

图4-7 利用ISE新建工程的示意图

再点击“Next”进入下一页,可以选择新建源代码文件,也可以直接跳过,进入下一页。第4页用于添加已有的代码,如果没有源代码,点击“Next”,进入最后一页,单击确认后,就可以建立一个完整的工程。

4.2.2 代码输入在工程管理区任意位置单击鼠标右键,在弹出的菜单中选择“New Source”命令,会弹出如图4-9所示的New Source对话框。

图4-9 新建源代码对话框

左侧的列表用于选择代码的类型,各项的意义如下所示:

- BMM File:

- ChipScope Definition and Connection File:在线逻辑分析仪ChipScope文件类型,具有独特的优势和强大的功能,将在M张进行讨论。

- IP(Coregen & Architecture Wizard):由ISE的IP Core生成工具快速生成可靠的源代码,这是目前最流行、最快速的一种设计方法,将在4.5节详细讨论。

- MEM File:

- Implementation Constraints File:约束文件类型。

- State Disgram:状态图类型。

- Test Bench Wavaform:测试波形类型。

- User Document:用户文档类型。

- Verilog Module:Verilog模块类型。

- Verilog Test Fixture:Verilog测试模块类型。

- VHDL Module:VHDL模块类型。

- VHDL Library:VHDL库类型。

- VHDL Packet:VHDL包类型。

- VHDL Test Bench:VHDL测试模块类型。

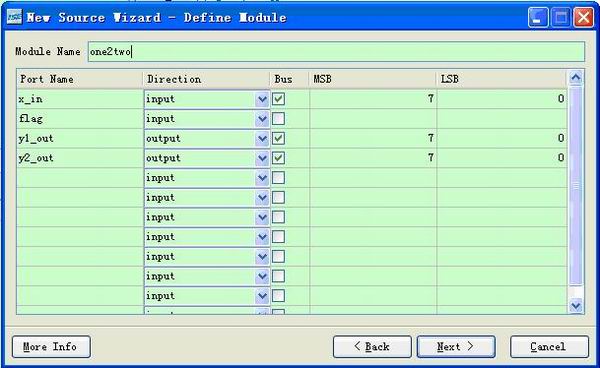

在代码类型中选择Verilog Module选项,在File Name文本框中输入one2two,单击Next进入端口定义对话框,如图4-10所示。

其中Module Name就是输入的“one2two”,下面的列表框用于对端口的定义。“Port Name”表示端口名称,“Direction”表示端口方向(可以选择为input、output或inout),MSB表示信号的最高位,LSB表示信号的最低位,对于单位信号的MSB和LSB不用填写。

定义了模块端口后,单击“Next”进入下一步,点击“Finish”按键完成创建。这样,ISE会自动创建一个Verilog模块的例子,并且在源代码编辑区内打开。简单的注释、模块和端口定义已经自动生成,所剩余的工作就是在模块中实现代码。填入的代码如下:

module one2two(x_in, flag, y1_out, y2_out);

input [7:0] x_in;

input flag;

output [7:0] y1_out;

output [7:0] y2_out;

// 以下为手工添加的代码

assign y1_out = flag ? x_in : 8'b0000_0000;

assign y2_out = flag ? 8'b0000_0000 : x_in;

endmodule

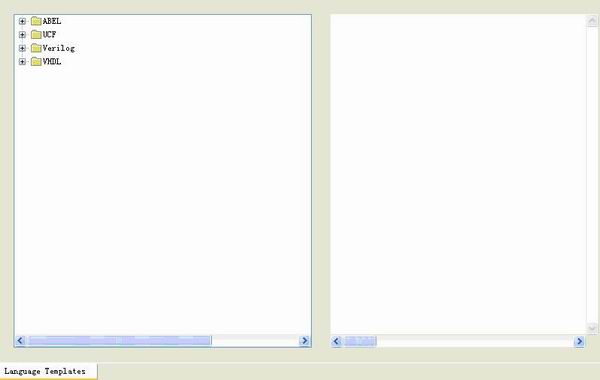

ISE中内嵌的语言模块包括了大量的开发实例和所有FPGA语法的介绍和举例,包括Verilog HDL/HDL的常用模块、FPGA原语使用实例、约束文件的语法规则以及各类指令和符号的说明。语言模板不仅可在设计中直接使用,还是FPGA开发最好的工具手册。在ISE工具栏中点击 图标,或选择菜单“Edit | Language Templates”,都可以打开语言模板,其界面如图4-11所示。

界面左边有4项:ABEL、UCF 、Verilog以及VHDL,分别对应着各自的参考资料。其中ABEL语言主要用于GAL和ISP等器件的编程,不用于FPGA开发。

以Verilog为例,点击其前面的“+”号,会出现Common Constructs、Device Primitive Instantiation、Simulation Constructs、Synthesis Constructs以及User Templates 5个子项。其中第1项主要介绍Verilog开发中所用的各种符号的说明,包括注释符以及运算符等。第2项主要介绍Xilinx 原语的使用,可以最大限度地利用FPGA的硬件资源。第3项给出了程序仿真的所有指令和语句的说明和示例。第4项给出了实际开发中可综合的Verilog语句,并给出了大量可靠、实用的应用实例, FPGA开发人员应熟练掌握该部分内容。User Templates项是设计人员自己添加的,常用于在实际开发中统一代码风格。

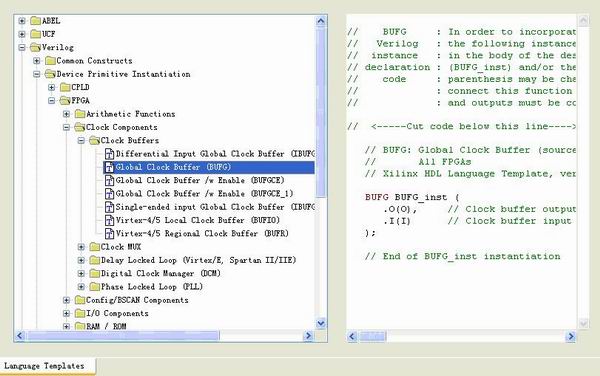

下面以调用全局时钟缓冲器模版为例,给出语言模板的使用方法。在语言模板中,选择“Device Primitive Instantiation FPGA Clock Components Clock Buffers Global Clock Buffer(BUFG)”,即可看到调用全局时钟缓冲的示例代码,如图4-12所示。

4.2.3 Xilinx IP Core的使用

1. Xilinx IP core基本操作

IP Core就是预先设计好、经过严格测试和优化过的电路功能模块,如乘法器、FIR滤波器、PCI接口等,并且一般采用参数可配置的结构,方便用户根据实际情况来调用这些模块。随着FPGA规模的增加,使用IP core完成设计成为发展趋势。

IP Core生成器(Core Generator)是Xilinx FPGA设计中的一个重要设计工具,提供了大量成熟的、高效的IP Core为用户所用,涵盖了汽车工业、基本单元、通信和网络、数字信号处理、FPGA特点和设计、数学函数、记忆和存储单元、标准总线接口等8大类,从简单的基本设计模块到复杂的处理器一应俱全。配合Xilinx网站的IP中心使用,能够大幅度减轻设计人员的工作量,提高设计可靠性。

Core Generator最重要的配置文件的后缀是.xco,既可以是输出文件又可以是输入文件,包含了当前工程的属性和IP Core的参数信息。

启动Core Generato有两种方法,一种是在ISE中新建IP类型的源文件,另一种是双击运行[开始] [程序] [Xilinx ISE 9.1i] [Accessories] [Core Generator]。限于篇幅,本节只以调用加法器IP Core为例来介绍第一种方法。

在工程管理区单击鼠标右键,在弹出的菜单中选择New Source,选中IP类型,在File Name文本框中输入adder(注意:该名字不能出现英文的大写字母),然后点击Next按键,进入IP Core目录分类页面,如图4-13所示。

图4-13 IP Core目录分类页面

下面以加法器模块为例介绍详细操作。首先选中“Math Funcation Adder & Subtracter Adder Subtracter v7.0”,点击“Next”进入下一页,选择“Finish”完成配置。这时在信息显示区会出现“Customizing IP...”的提示信息,并弹出一个“Adder Subtracter”配置对话框,如图4-14所示。

图4-14 加法器IP Core配置对话框

然后,选中adder,设置位宽为16,然后点击“Generate”,信息显示区显示Generating IP...,直到出现Successfully generated adder的提示信息。此时在工程管理区出现一个“adder.xco”的文件。这样加法器的IP Core已经生成并成功调用。

IP Core在综合时被认为是黑盒子,综合器不对IP Core做任何编译。IP Core的仿真主要是运用Core Generator的仿真模型来完成的,会自动生成扩展名为.v的源代码文件。设计人员只需要从该源文件中查看其端口声明,将其作为一个普通的子程序进行调用即可。下面给出加法器的应用实例。

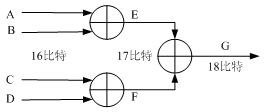

例4-1 调用加法器的IP core,并用其实现图4-15所示的2级加法树。

图4-15 2级加法器示意图

按照本节介绍的步骤生成2个加法器的IP core Add16和Add17,前者用于实现第1级的加法,后者用于实现第2级加法,对应的代码为:

module addertree(clk, a1, a2, b1, b2, c);

input clk;

input [15:0] a1;

input [15:0] a2;

input [15:0] b1;

input [15:0] b2;

output [17:0] c;

wire [16:0] ab1, ab2;

adder16 adder16_1(.A(a1),

.B(a2),

.Q(ab1),

.CLK(clk));

adder16 adder16_2(.A(b1),

.B(b2),

.Q(ab2),

.CLK(clk));

adder17 adder17(.A(ab1),

.B(ab2),

.Q(c),

.CLK(clk));

endmodule

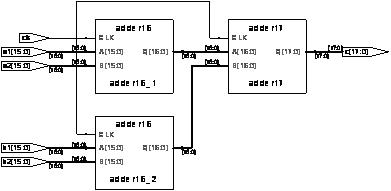

上述程序经过综合后,得到如图4-16所示的RTL级结构图。

图4-16 2级加法树的RTL结构图

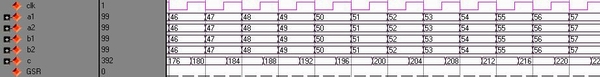

经过ModelSim 6.2b仿真测试,得到的功能波形图如图4-17所示。由于每一级加法器会引入一个时钟周期的延迟,因此,两级加法器就会引入2个时钟的周期,可以看出,仿真结果和设计分析的结果是一样的。

图4-17 2级加法树仿真结果示意图

Xilinx公司提供了大量的、丰富的IP Core资源,究其本质可以分为两类:一是面向应用的,和芯片无关;还有一种用于调用FPGA底层的宏单元,和芯片型号密切相关。下面分别对这两类给出数字频率合成器模块DDS的调用实例。

2. DDS模块IP Core的调用实例

- DDS算法原理

DDS技术是一种新的频率合成方法,是频率合成技术的一次革命,最早由JOSEPH TIERNEY等3人于1971年提出,但由于受当时微电子技术和数字信号处理技术的限制,DDS技术没有受到足够重视,随着数字集成电路和微电子技术的发展,DDS技术日益显露出它的优越性。

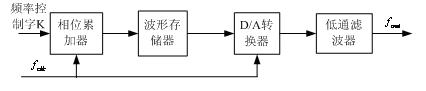

DDS的工作原理为:在参考时钟的驱动下,相位累加器对频率控制字进行线性累加,得到的相位码对波形存储器寻址,使之输出相应的幅度码,经过模数转换器得到相应的阶梯波,最后再使用低通滤波器对其进行平滑,得到所需频率的平滑连续的波形,其结构如图4-18所示。

图4-18 DDS的结构框图

相位累加器由N位加法器与N位累加寄存器级联构成,结构如图4-19所示。每来一个时钟脉冲fclk,加法器将频率控制字K与累加寄存器输出的累加相位数据相加,把相加后的结果送至累加寄存器的数据输入端。累加寄存器将加法器在上一个时钟脉冲作用后所产生的新相位数据反馈到加法器的输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。由此可以看出,相位累加器在每一个时钟脉冲输入时,把频率控制字累加一次,相位累加器输出的数据就是合成信号的相位,相位累加器的溢出频率就是DDS输出的信号频率。用相位累加器输出的数据作为波形存储器(ROM)的相位取样地址,这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出,完成相位到幅值转换.

图4-19 DDS相位累加器

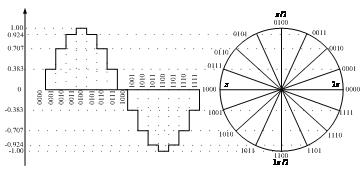

波形存储器所储存的幅度值与余弦信号有关。余弦信号波形在一个周期内相位幅度的变化关系可以用图4-20中的相位圆表示,每一个点对应一个特定的幅度值。一个N位的相位累加器对应着圆上 个相位点,其相位分辨率为 。若 ,则共有16种相位值与16种幅度值相对应,并将相应的幅度值存储于波形存储器中,存储器的字节数决定了相位量化误差。在实际的DDS中,可利用正弦波的对称性,可以将 范围内的幅、相点减小到 内以降低所需的存储量,量化的比特数决定了幅度量化误差。

图4-20 三角函数相位与幅度的对应关系

波形存储器的输出送到 D/A 转换器,D/A 转换器将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号。低通滤波器用于滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。DDS 在相对带宽、频率转换时间、高分辨力、相位连续性、正交输出以及集成化等一系列性能指标方面远远超过了传统频率合成技术所能达到的水平,为系统提供的信号源优于模拟信号源。

DDS模块的输出频率 是系统工作频率 、相位累加器比特数N以及频率控制字K三者的一个函数,其数学关系由式(4.1)给出。

(4.1)

(4.1)

它的频率分辨率,即频率的变化间隔为:

(4.2)

(4.2)

- DDS IP Core的调用

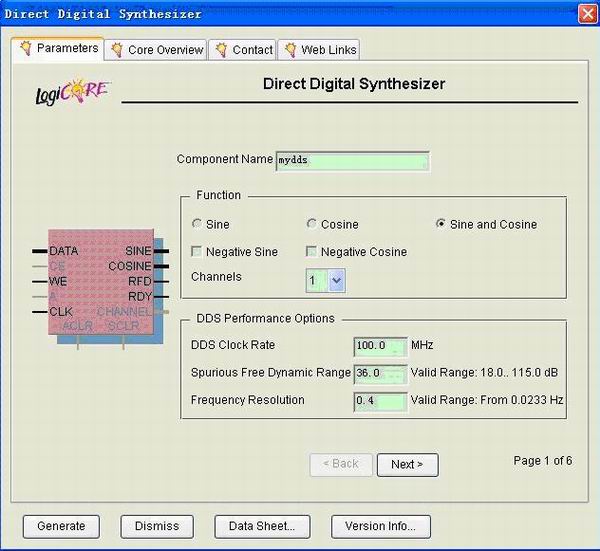

DDS模块IP Core的用户界面如图4-21所示。该IP Core支持余弦、正弦以及正交函数的输出,旁瓣抑制比的范围从18dB 到115dB,最小频率分辨率为0.02Hz,可同时独立支持16个通道。其中的查找表既可以利用分布式RAM,也可利用块RAM。

图4-21 DDS IP Core的用户界面

DDS模块的信号端口说明如下:

(1)CLK:输入信号,DDS模块的工作时钟,对DDS输出信号的频率和频率分辨率有很大的影响。即式(5.40)中的 。

(2)A:输入信号,由于DDS模块的相位增量存储器和相位偏置寄存器共用一个数据通道,A端口信号用于片选相位增量寄存器和偏置寄存器。当A端口的最高位为1时,相位偏置寄存器被选中;当其为0时,则选中相位增量寄存器。其余的低4位比特用于片选DDS的输出通道,最多可以输出 16路信号。

(3)WE:输入信号,写有效控制信号,高有效。只有当WE为高时,DATA端口的数值才能被写入相应的寄存器中。

(4)DATA:输入信号,时分复用的数据总线,用于配置相位增量寄存器和相位偏置寄存器。

(5)ACLR:输入信号,异步的清空信号,高有效。当ACLR等于1时,DDS模块内部所有的寄存器都被清空,RDY信号也会被拉低。

(6)SCLR:输入信号,同步的清空信号,高有效。当SCLR等于1时,DDS模块内部所有的寄存器都被清空,RDY信号也会被拉低。

(7)RDY:输出信号,输出握手信号。当其为高时,标志输出信号已经准备好。

(8)CHANNEL:输出信号,输出通路的下标。用于表明当前时刻输出端为哪一路输出,其位宽由通道数决定。

(9)SINE:输出信号,用于输出正弦的时间序列。

(10)COSINE:输出信号,用于输出余弦的时间序列。

例4-2 使用DDS IP Core实例化一个4MHz,分辨率为0.1Hz,带外抑制比为60dB的正、余弦信号发生器,假设工作时钟为100MHz。

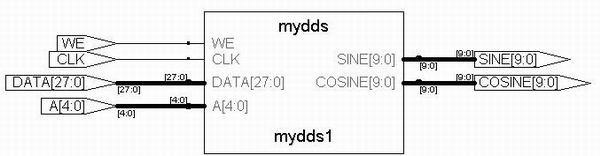

IP Core直接生成DDS的Verilog模块接口为:

module mydds(

DATA,

WE,

A,

CLK,

SINE,

COSINE

); // synthesis black_box

input [27 : 0] DATA;

input WE;

input [4 : 0] A;

input CLK;

output [9 : 0] SINE;

output [9 : 0] COSINE;

……

endmodule

在使用时,直接调用mydds模块即可,如

module dds1(DATA, WE, A, CLK, SINE, COSINE);

input [27 : 0] DATA; //经过计算,DATA= 10737418.

input WE;

input [4 : 0] A;

input CLK;

output [9 : 0] SINE;

output [9 : 0] COSINE;

mydds mydds1(

.DATA(DATA),

.WE(WE),

.A(A),

.CLK(CLK),

.SINE(SINE),

.COSINE(COSINE)

);

endmodule

上述程序经过综合后,得到如图4-22所示的RTL级结构图。

图4-22 DDS模块的RTL结构图

经过ModelSim仿真测试,得到的功能波形图如图4-23所示:

图4-23 DDS模块的局部功能仿真波形图

注意:经过笔者大量验证发现,在ISE 8.2版中使用DDS IP core时,只有采用wire型的变量控制DDS才能在ModelSim中得到正确结果,使用reg型的变量不能成功操控该IP core。

转自:http://bbs.eccn.com/viewthread.php?tid=93673&extra=&page=1

- 第4章 ISE开发环境使用指南[FPGA开发实用教程]——第2节 HDL代码输入

- 第4章 ISE开发环境使用指南[FPGA开发实用教程]——第3节 基于ISE的开发流程

- 第4章 ISE开发环境使用指南[FPGA开发实用教程]——第1节 ISE套件的介绍与安装

- 第4章 ISE开发环境使用指南[FPGA开发实用教程]——4.3.5 功耗分析以及XPower的使用

- 第4章 建立开发环境

- 第4章 建立开发环境

- 第2章 Openwrt开发环境搭建

- XNA开发实用教程——游戏最基本代码

- JSP大学实用教程(第2版)代码一

- 第2章第5节 Wanlix的开发环境

- 第1章 搭建s2sm开发环境

- XNA开发实用教程——图片

- XNA开发实用教程——添加文字

- XNA开发实用教程——键盘输入事件

- 第 4 章 选择合适的Python开发环境

- 第4章 协议栈相关开发环境搭建

- 第2章 windows下搭建开发环境

- FPGA开发之modelsim和ISE的联合仿真

- 代码签名证书FAQ

- MultiByteToWideChar和WideCharToMultiByte用法详解 .

- 将点分式的IP地址转换成长整型

- Adapter简介 SimpleAdapter

- C51资料收集汇总

- 第4章 ISE开发环境使用指南[FPGA开发实用教程]——第2节 HDL代码输入

- MapReduce编程模型的要点

- 如何注册公司

- 不用获得焦点也能实现跑马灯效果的textView

- Session实例:一次性验证码

- HDOJ 2049 不容易系列之(4)——考新郎

- android横竖屏切换、键盘推出状态改变的处理

- Marty Cagan:产品管理与软件开发的关系

- Jquery AJAX POST和GET区别