SPI协议通信

来源:互联网 发布:双模卡写卡软件 编辑:程序博客网 时间:2024/04/28 19:16

SPI接口介绍

SPI总线协议

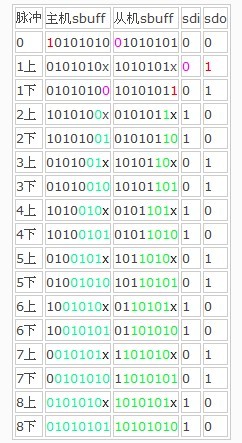

SPI是一个环形总线结构,由ss(cs)、sck、sdi、sdo构成,其时序其实很简单,主要是在sck的控制下,两个双向移位寄存器进行数据交换。

这样就完成了两个寄存器8位的交换,上面的上表示上升沿、下表示下降沿,sdi、sdo相对于主机而言的。其中ss引脚作为主机的时候,从机可以把它拉底被动选为从机,作为从机的是时候,可以作为片选脚用。根据以上分析,一个完整的传送周期是16位,即两个字节,因为,首先主机要发送命令过去,然后从机根据主机的名准备数据,主机在下一个8位时钟周期才把数据读回来

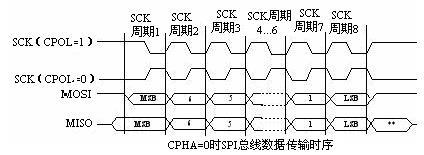

SPI 总线是Motorola公司推出的三线同步接口,同步串行3线方式进行通信:一条时钟线SCK,一条数据输入线MOSI,一条数据输出线MISO;用于 CPU与各种外围器件进行全双工、同步串行通讯。SPI主要特点有:可以同时发出和接收串行数据;可以当作主机或从机工作;提供频率可编程时钟;发送结束中断标志;写冲突保护;总线竞争保护等。图3示出SPI总线工作的四种方式,其中使用的最为广泛的是SPI0和SPI3方式(实线表示):

图2

SPI总线接口及时序

SPI 功能模块的设计

根据功能定义及SPI的工作原理,将整个IP Core分为8个子模块:uC接口模块、时钟分频模块、发送数据FIFO模块、接收数据FIFO模块、状态机模块、发送数据逻辑模块、接收数据逻辑模块以及中断形式模块。

深入分析SPI的四种传输协议可以发现,根据一种协议,只要对串行同步时钟进行转换,就能得到其余的三种协议。为了简化设计规定,如果要连续传输多个数据,在两个数据传输之间插入一个串行时钟的空闲等待,这样状态机只需两种状态(空闲和工作)就能正确工作。

- SPI协议通信

- SPI通信

- SPI通信

- spi通信

- SPI通信

- SPI通信

- SPI通信

- SPI通信

- SPI通信

- SPI通信

- SPI通信

- 两单片机通过 SPI 通信的软件协议设计概述

- FPGA 学习之路(九)SPI协议通信

- 蓝牙BLE基础:CC2541通信系列之模拟SPI协议

- SPI协议

- SPI 协议

- SPI协议

- SPI协议

- POJ1322 Chocolate DP

- 常用超低阻值采样电阻阻值一览表

- 分享10个JavaScript在线Debugging工具

- Ubuntu 11.04下自定义截图快捷键

- 12-1-21进步一小点

- SPI协议通信

- .NET版的WebGoat

- 深入理解const char*p,char const*p,char *const p,const char **p,char const**p,char *const*p,char**const p

- zoj 1201 inversion(我真是弱爆了)

- hdu 3343 Legal or Not 拓扑排序(容易题)

- Windows程序设计__孙鑫C++Lesson1《Windows内部运行原理》

- ora-15077,ASM磁盘组不能挂载

- linux HID驱动分析

- Servlet 3.0 新特性详解