PCI总线(一)

来源:互联网 发布:linux服务器全球份额 编辑:程序博客网 时间:2024/04/29 03:41

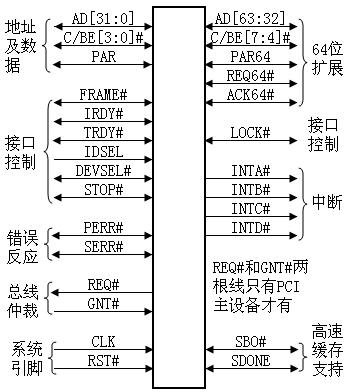

1.PCI总线管脚功能

PCI主设备最少需要49根线,从设备最少需要47根线,剩下的线可选。在介绍PCI管脚功能前,先来说明下PCI管脚信号的类型

in:输入信号;

out:输出信号;

t/s:双向三态信号(Tri-state),无效时为高组态;

s/t/s:持续三态信号(Sustained Tri-state),每次由且只由一个单元拥有并驱动的低有效双向、三态信号。驱动一个s/t/s信号到低的单元在释放该信号浮空之前必须要将它驱动到高电平至少一个周期。这个特点很重要,在后面我们分析PCI信号质量案例的时候会用到;

o/d:漏极开路输出(Open Drain);

#:此符号代表该信号在低电平时有效。

PCI总线引脚图如下所示。

实际使用中需要上拉的信号有:FRAME#, TRDY#, IRDY#, DEVSEL#, STOP#, PERR#, SERR#, LOCK#, REQ64#, ACK64#, REQ#, GNT#, AD[63:32], C/BE[7:4], PAR64等,上拉电阻一般为10kohm,未使用的PCI管脚也要处理,避免悬空。不需要上拉的信号有AD[31:0], C/BE[3:0], PAR, IDSEL, CLK。

1).系统引脚

CLK:in,系统时钟,为所有PCI上的传输及总线仲裁提供时序。除RST#外,所有PCI信号都在CLK信号的上升沿采样。

RST#:in,异步复位信号。

2).地址及数据引脚

AD[31:0]:t/s,地址数据复用引脚。FRAME#开始变为有效的那个时钟周期内AD[31:0]上传输的是地址。对于配置空间和存储空间,这是一个双字节地址,对于I/O空间,这个一个单字节地址。传输数据时,AD[7:0]为最低字节数据。

C/BE[3:0]#:t/s,总线命令和字节允许复用引脚。在AD[31:0]上传输地址的时候,C[3:0]上传输的是总线命令,AD[31:0]上传输数据的时候,BE[3:0]#用作字节允许,表示哪些通道上的数据是有效的。BE0#对应最低字节。

PAR:t/s,AD[31:0]和C/BE[3:0]#上的数据偶效验。PAR与AD[31:0]有相同的时序,但延迟一个时钟,在地址段后一个时钟,PAR稳定并有效;对于数据段,在写传输中,PAR在IRDT#有效一个时钟稳定并有效,而在读传输中,PAR在TRDY#有效后一个时钟周期稳定并有效。一旦PAR有效,它必须保持有效直到当前数据段完成后一个时钟。在地址段和写数据段,主PCI设备驱动PAR,在读数据段,目标从PCI 设备驱动PAR。

3).接口控制引脚

FRAME#:s/t/s,帧开始信号。由当前总线主设备驱动,以说明一个操作的开始和延续。FRAME#有效,说明总线开始传输,当FRAME#维持有效时,说明总线传输继续进行,当FRAME#无效时,说明传送的最后一个字节正在进行。

IRDY#:s/t/s,启动者准备好信号(Initiator Ready)。说明传输的启动者完成当前数据传输的能力。在读操作中,IRDY#有效说明总线主设备已准备好接收收据。在写操作中,它说明AD[3:0]上已有有效数据。在IRDY#和TRDY#都有效的时钟周期完成数据传输。在IRDY#和TRDY#都有效之前,需要插入等待状态。

TRDY#:s/t/s,目标设备准备就绪(Target Ready)。说明传输的目标设备完成当前的数据传输能力。在写操作中,TRDY#有效说明目标设备已经准备好接收数据。在读操作中,它说明AD[31:0]上已有有效数据。

STOP#:s/t/s,停止信号。说明当前的目标设备要求总线主设备停止当前传输。

LOCK#:s/t/s,锁定信号。

IDSEL:in,初始化设备选择(Initialization Device Select)。在配置空间读写操作中,用作片选。

DEVSEL#:s/t/s,设备选择。当驱动有效时,说明驱动它的设备已将其地址解码为当前操作的目标设备。

4).仲裁引脚

REQ#:t/s,申请。向仲裁器说明该单元想使用总线。这是一个点对点的信号,每个总线主设备都有自己的REQ#。

GNT#:t/s,允许。仲裁器向申请单元说明其对总线的操作已被允许。这是一个点对点信号,每个总线主设备都有自己的GNT#。

5).错误反馈引脚

PERR#:s/t/s,奇偶校验错误(Parity Error)。该引脚用于反馈在除特殊周期外的其他传送过程中的数据奇偶校验错误。PERR#维持三态,在检测到奇偶校验错误后,在数据结束后两个时钟周期,由接收数据的单元驱动PERR#有效。并至少持续一个时钟周期。只有发出DEVSEL#的单元才能发出PERR#。

SERR#:o/d,系统错误(System Error)。用于反馈地址奇偶校验错误、特殊周期命令中的数据奇偶校验错误和将引起重大事故的其他灾难性的系统错误。

6).中断引脚

INTA#, INTB#, INTC#, INTD#:o/d,中断输出。

7).高速缓存支持引脚

一个能高速缓存的PCI存储器必须利用这两条高速缓存支持引脚作为输入,以支持写通(write-through)和回写(write-back)。如果可高速缓存的存储器是位于PCI上,则连接回写高速缓存到PCI的桥路必须利用这两条引脚,且作为输出。连接写通高速缓存的桥路可以只使用一条引脚SDONE。

SBO#:in/out,监视补偿。当其有效时,说明对某条变化线的一次命中。当SBO#无效而SDONE有效时,说明了一次“干净”的监视结果。

SDONE: in/out,监视进行。表明对当前操作的监视状态。当其无效时,说明监视结果仍未定。当有效时,说明监视已有结果。

8).64位总线扩充引脚

AD[63:32]:t/s,地址数据复用引脚提供32个附加位。在一个地址段,传送64位地址的高32位。在数据段,传送64位中的高32位。

C/BE[7:4]#:t/s,总线命令和字节允许复用引脚。

REQ64#:s/t/s,请求64位传输。当其被当前总线主设备有效驱动时,说明总线主设备想作64位传输。

ACK#:s/t/s,应答64位传送。在当前操作所寻址的目标设备有效驱动该信号时,说明目标设备能够进行64位传输,ACK#和DEVSEL#有相同的时序。

PAR64:t/s,高双字偶校验。

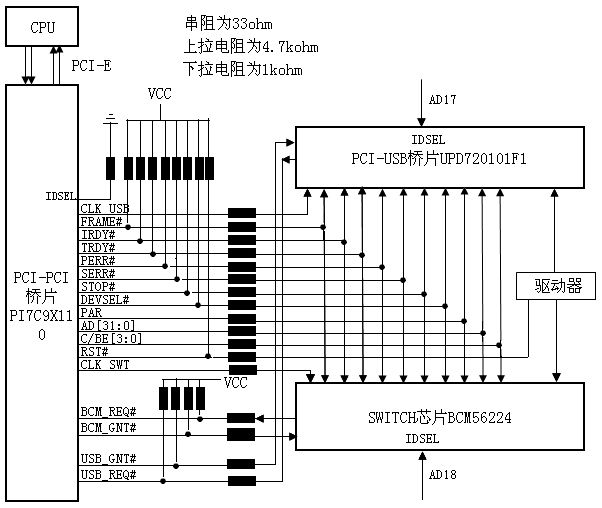

2. PCI总线的典型接法

下图为PCI总线的典型接法,

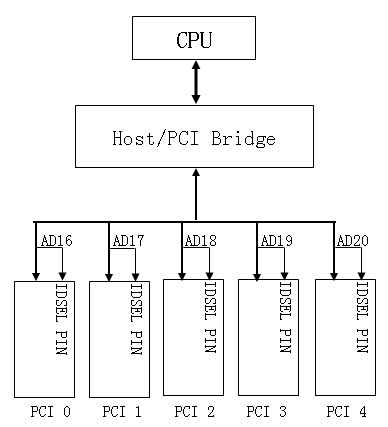

3.PCI总线上IDSEL管脚的处理方式

主PCI桥片的IDSEL管脚一般通过电阻下拉到地,从PCI设备的IDSEL管脚和AD[11:31]相连,每个PCI从设备连接其的一根,且不能重复。如下图所示。

4.PCI信号的驱动方式

PCI信号为半波驱动方式,为了更好的说明什么是半波驱动方式,下面我用一个仿真实例来说明。下图为仿真链路。

仿真出来的波形如下图所示。(示意图)

从上图可以看出,PCI_OUT_3.3V输出先是以大约2.3V的半幅度来驱动总线,经过大约2ns延迟后,信号到达接收端,接收端阻抗不匹配,将信号反射回始端,反射信号经过2ns的延迟后到达始端,驱动信号与反射信号在始端出现叠加,使PCI_OUT_3.3V在大约4ns的位置达到全幅度3.3V。之后经过短暂振荡后趋于平衡。由于大多数PCI器件片内都内置了限幅器件,所以PCI信号在不在始端添加串行匹配电阻都可以使PCI信号很快平稳。只是加串阻后,信号幅度更低,使PCI器件的使用寿命更长。

- PCI总线(一)

- PCI总线(一)

- PCI总线学习(一)---> PCI概述

- PCI总线协议(一)

- PCI总线学习笔记(一)

- PCI总线(二)

- PCI总线(二)

- PCI 总线操作一 :总线command

- PCIe总线学习笔记(一、PCI基础知识简介)

- PCIe总线学习笔记(一、PCI基础知识简介)

- PCI总线学习(五)---> PCI中断

- PCI总线学习(二)---> PCI总线仲裁

- PCI总线学习(三)---> PCI总线命令

- pci总线原理(转)

- PCI总线进阶(二)

- pci总线扫描操作一(pci桥操作)

- PCI总线

- PCI总线

- 网页oject播放器

- jquery 插件之 floattextbox 修改版

- 串口通讯奇偶校验位的设置导致数据错误

- 3张表关联

- .NET程序员,你属于哪个级别

- PCI总线(一)

- 上班那些事---学习js

- WEB开发中图片取颜色,取图片文字的字体工具

- LTIB 详解(一) 安装与卸载

- ORDER BY CHARINDEX 语法

- 搬了新家,转让一批书。

- 图片下载工具类:BitmapUtil

- 数据库设计经验谈

- WIN32下的网络初始化