MP系统下的三种中断模式 .

来源:互联网 发布:网络信息安全防护体系 编辑:程序博客网 时间:2024/05/01 18:51

3.6.2.1 PIC Mode

PIC Mode is software compatible with the PC/AT because it actually employs the same hardware

interrupt configuration. As Figure 3-2 illustrates, the hardware for PIC Mode bypasses the APIC

components by using an interrupt mode configuration register (IMCR). This register controls

whether the interrupt signals that reach the BSP come from the master PIC or from the local APIC.

Before entering Symmetric I/O Mode, either the BIOS or the operating system must switch out of

PIC Mode by changing the IMCR.

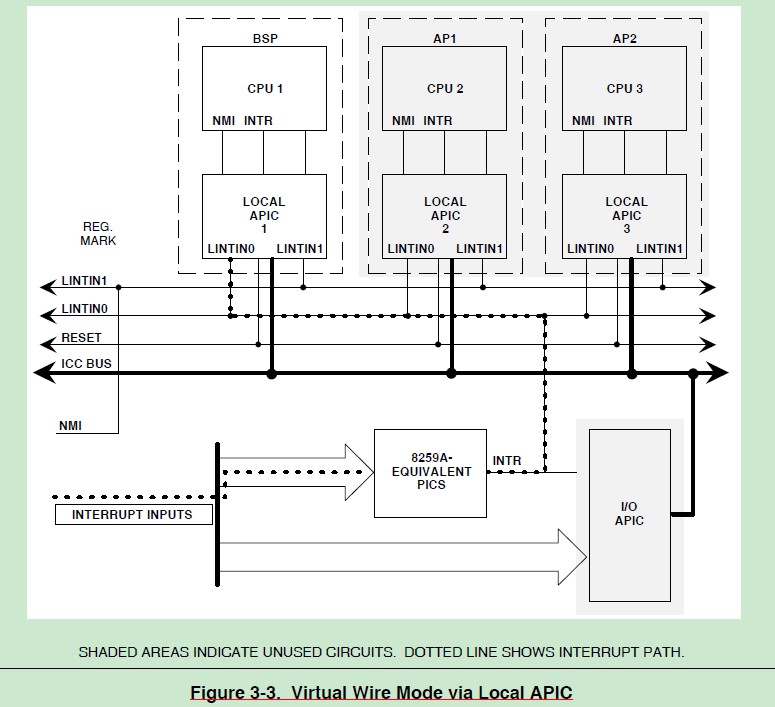

3.6.2.2 Virtual Wire Mode

In Virtual Wire Mode, as shown in Figure 3-3, the 8259A-equivalent PIC fields all interrupts, and

the local APIC of the BSP becomes a virtual wire, which delivers interrupts from the PIC to the

BSP via the local APIC’s local interrupt 0 (LINTIN0). The LINTIN0 pin of the local APIC is

programmed as ExtINT, specifying to the APIC that the PIC is to serve as an external interrupt

controller. Whenever the local APIC finds that a particular interrupt is of type ExtINT, it asserts

the ExtINTA transaction along with the PINT interrupt to the processor. In this case, the I/O APIC

is not used.

Figure 3-3 shows how Virtual Wire Mode can be implemented through the BSP’s local APIC. It is

also permissible to program the I/O APIC for Virtual Wire Mode, as shown in Figure 3-4. In this

case the interrupt signal passes through both the I/O APIC and the BSP’s local APIC.

3.6.2.3 Symmetric I/O Mode

Some MP operating systems operate in Symmetric I/O Mode. This mode requires at least one I/O

APIC to operate. In this mode, I/O interrupts are generated by the I/O APIC. All 8259 interrupt

lines are either masked or work together with the I/O APIC in a mixed mode. See Figure 3-5 for

an overview of Symmetric I/O Mode.

- MP系统下的三种中断模式

- MP系统下的三种中断模式

- MP系统下的三种中断模式 .

- MP系统下的三种中断模式

- 51单片机的中断系统(三)

- 非常系统的KMP\MP算法讲解

- Linux2.6中断下半部分的三种实现机制---软中断/tasklet/工作队列

- Linux2.6中断下半部分的三种实现机制---软中断/tasklet/工作队列

- ARM2200 下的中断编程三

- 《一个操作系统的实现》(三):4.中断和异常&5.保护模式下的I/O

- vmware 下的三种网络模式

- 一篇保护模式下处理实模式中断的硬盘中断处理程序文章(转)

- ARM体系结构笔记①---(ARM的7种模式、寄存器、存储空间、指令、中断、最小系统)

- Linux2.6中断下半部分的三种实现机制---工作队列

- Linux2.6中断下半部分的三种实现机制---工作队列 .

- 实例:中断的下半部分之三work_queue

- arm的三种中断状态

- 中断下半部的三种机制

- java构造顺序

- linux下杀死进程(kill)的N种方法

- Integer.parseInt()和Integer.valueOf()的区别

- 如何拷贝带'/0'的字符串

- Interrupt--PIC--APIC .

- MP系统下的三种中断模式 .

- C#程序集使用强名字(Strong Name)签名/强名称签名

- NC创建表空间及数据导入导出语句

- log4j写入mysql数据库

- HP-UX下的抓包工具nettl

- Android 累计未读通知的数量

- 网址

- extern的使用

- 第三章、一些基本数据结构使用和解析(iOS学习笔记,从零开始。)