关于计算机体系结构之RAM

来源:互联网 发布:芭芭拉史翠珊 知乎 编辑:程序博客网 时间:2024/04/28 15:51

相关链接:http://www.oschina.net/translate/what-every-programmer-should-know-about-memory-part1?p=4#comments

为什么在同一台机器中有不同的RAM?或者说得更详细一点,为什么既有静态RAM

(SRAM {SRAM还可以表示「同步内存」。}),又有动态RAM(DRAM)。功能相同,

前者更快。那么,为什么不全部使用SRAM?答案是,代价。无论在生产还是在使用上,

SRAM都比DRAM要贵得多。生产和使用,这两个代价因子都很重要,后者则是越来越重要。

为了理解这一点,我们分别看一下SRAM和DRAM一个位的存储的实现过程。

2.1.1 静态RAM

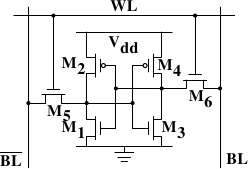

图2.6 6-T静态RAM

图展示了6晶体管SRAM的一个单元。核心是4个晶体管M1-M4,它们组成两个交叉耦合的反相器。

它们有两个稳定的状态,分别代表0和1。只要保持Vdd有电,状态就是稳定的。

当需要访问单元的状态时,升起字访问线WL。BL和BL上就可以读取状态。如果需要覆盖状态,

先将BL和BL设置为期望的值,然后升起WL。由于外部的驱动强于内部的4个晶体管,所以旧状态会被覆盖。

维持状态需要恒定的电源。

升起WL后立即可以读取状态。信号与其它晶体管控制的信号一样,是直角的(快速在两个状态间变化)。

状态稳定,不需要刷新循环。

动态RAM

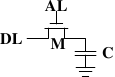

动态RAM比静态RAM要简单得多。图2.5展示了一种普通DRAM的结构。它只含有一个晶体管和一个电容器。

显然,这种复杂性上的巨大差异意味着功能上的迥异。

图2.5 1-T动态RAM

动态RAM的状态是保持在电容器C中。晶体管M用来控制访问。如果要读取状态,升起访问线AL,

这时,可能会有电流流到数据线DL上,也可能没有,取决于电容器是否有电。如果要写入状态,先设置DL,

然后升起AL一段时间,直到电容器充电或放电完毕。

动态RAM的设计有几个复杂的地方。由于读取状态时需要对电容器放电,所以这一过程不能无限重复,

不得不在某个点上对它重新充电。

更糟糕的是,为了容纳大量单元(现在一般在单个芯片上容纳10的9次方以上的RAM单元),电容器的容量

必须很小(0.000000000000001法拉以下)。这样,完整充电后大约持有几万个电子。即使电容器的电阻很大(若干兆欧姆),仍然只需很短的时间就会耗光电荷,称为「泄漏」。

这种泄露就是现在的大部分DRAM芯片每隔64ms就必须进行一次刷新的原因(动态)。在刷新期间,

对于该芯片的访问是不可能的,这甚至会造成半数任务的延宕。(访问速度比静态内存小)

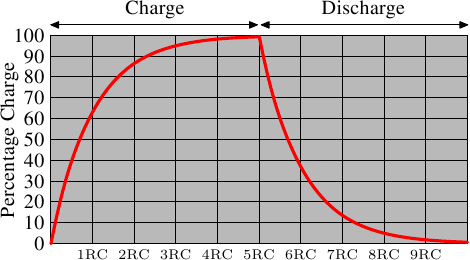

这就意味着需要一些时间(时间长短取决于电容C和电阻R)来对电容进行冲放电。另一个负面作用是,

信号放大器的输出电流不能立即就作为信号载体使用。图2.6显示了冲放电的曲线,x轴表示的是单位时间下的R*C

与静态RAM可以即刻读取数据不同的是,当要读取动态RAM的时候,必须花一点时间来等待电容的冲放电完全。

这一点点的时间最终限制了DRAM的速度。

当然了,这种读取方式也是有好处的。最大的好处在于缩小了规模。一个动态RAM的尺寸是小于静态RAM的。

这种规模的减小不单单建立在动态RAM的简单结构之上,也是由于减少了静态RAM的各个单元独立的供电部分。

以上也同时导致了动态RAM模具的简单化。

综上所述,由于不可思议的成本差异,除了一些特殊的硬件(包括路由器什么的)之外,我们的硬件大多是使用DRAM的。- 关于计算机体系结构之RAM

- 关于计算机体系结构的一点思考。

- 关于计算机体系结构的一点思考

- 计算机体系结构

- 计算机体系结构

- 计算机体系结构

- 计算机体系结构

- 计算机体系结构

- 计算机体系结构

- 计算机体系结构

- 计算机体系结构

- 计算机体系结构

- 计算机体系结构

- 计算机体系结构

- 计算机体系结构

- 计算机体系结构

- 计算机体系结构

- 计算机体系结构

- SDUT 第九周周赛

- 黑马程序员-数组

- 几个OJ链接

- Judging Olympia

- Stanford ML - Lecture 5 - Neural Networks: Learning

- 关于计算机体系结构之RAM

- 第一个windows8应用程序

- PHP安装eAccelerator加速器

- 如何在C/C++中动态分配二维数组

- Spring aop拦截器

- JAVA基础知识

- java中String Date Timestamp Calendar 之间的关系及转换

- com使用自定义数据类型(UDT) [转]

- MVC模式的好处