Zedboard-一些常见的IP核整理(AXI-Interconnect和AXI VDMA)

来源:互联网 发布:苹果最新软件源 编辑:程序博客网 时间:2024/06/05 13:21

一些常见的IP核整理(AXI-Interconnect和AXI VDMA)

AXI-INTERCONNECT

这个IP核是经常用到的,当我们在PL中增加某些IP核时,默认的选项是自动连接到processing_system_v7_0中,而选择这个后,会自动生成一个AXI INTERCONNECT将GP0或者GP1和IP核连接在一起,那么具体AXI-INTERCONNECT是做什么的呢?

在赛灵思提供的官方文档PG059中,它是这样描述的:

AXI Interconnect核心连接1个或者多个AXI内存映射的控制设备到1个或者多个内存映射的从设备中,另外,它格外强调AXI interconnect核心仅仅进行内存映射的设备之间的传输。

AXI Interconnect核由许多IP核实例组成(基础的IP核)

AXI 允许任意AXI 主或从设备连接到它上,另外可以定制数据宽度、时钟频率和AXI子协议(AXI4,AXI3),这些基础IP核包括:

AXI Crossbar 连接一个或多个类似的AXI内存映射主设备到一个或多个相似的从设备

AXI数据宽度转换器

AXI时钟转换器:转换不同时钟

AXI协议转换器:AXI4、AXI3或者AXI4-LITE之间的转换

AXI数据FIFO

AXI寄存器切片

其中最核心的是AXI Crossboar。

I/O 信号

比较重要的是两个信号:一个是ACLK,另一个是ARESETN

分别是Crossbar的时钟输入信号和复位信号(低有效)

AXI VDMA:

提供内存和AXI流视频类型的目标外设之间的高带宽存储访问,这类目标外设包括支持AXI4-流视频协议的设备。初始化、状态和管理寄存器通过AXI4-Lite从接口访问。

很多视频应用需要帧缓冲来处理帧速率变化,图像尺寸变化(拉伸),AXI VDMA被设计用来允许AXI4-流接口和AXI4内存映射接口之间的高带宽访问

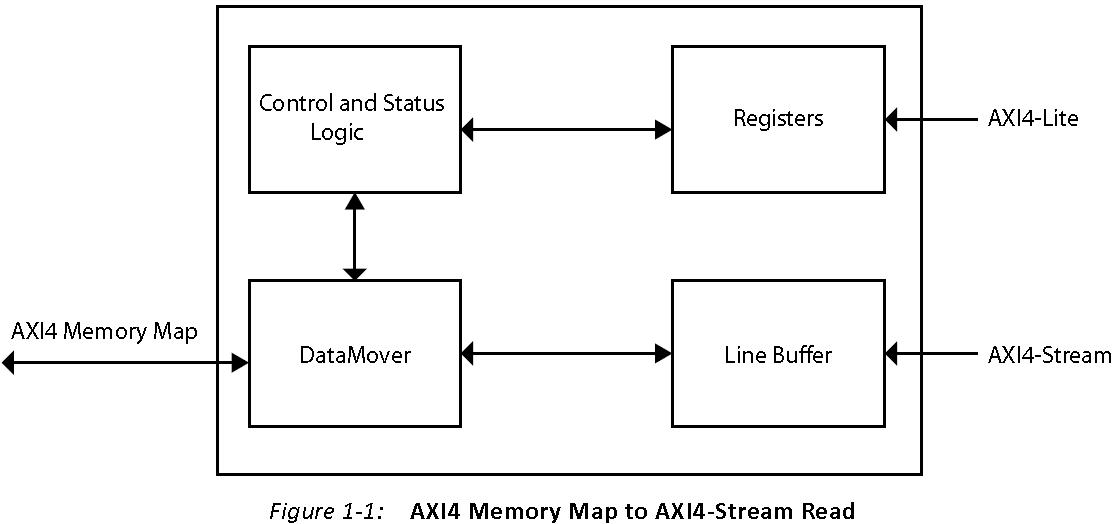

图1-1说明了AXI VDMA之间的数据通路

寄存器通过AXI4-Lite接口配置完之后,控制/状态逻辑块生成合适的命令给Datamover来初始化AXI4内存映射控制接口的写和读命令。

一个可配置的异步行缓冲用来处理内存映射和流处理接口的不同频率之间的差异。

在写通道上,AXI VDMA在AXI4-流从属接口上接收帧并把它写入到使用AXI4内存映射控制接口的系统内存中。写通道即是S2MM通道。

在读通道上,AXI VDMA使用AXI4内存映射控制接口来从系统内存中读取帧数据,并把它输出到AXI4流控制接口上。读通道指的是MM2S通道

另外有一个三帧缓冲例子,三帧缓冲或者删除/增加帧同步器是一个AXI VDMA的常见应用。三帧缓冲能够被用来在两个不同的时钟域间不间断的传递图像帧,一般的三帧缓冲使用3个不同帧存储来写或者读内存,在任何时候都不允许读写相同位置的帧数据,这样就避免了传输间断。

- Zedboard-一些常见的IP核整理(AXI-Interconnect和AXI VDMA)

- ZedBoard--(6)利用Vivado HLS生成AXI接口的IP核

- 基于AXI VDMA的图像采集系统

- AXI VDMA使用

- ZedBoard学习手记(二) 开发自定义AXI总线外设IP核——以LED和开关为例

- Zedboard自定义AXI总线IP详解(多图)

- [转]基于AXI VDMA的图像采集系统

- 自定义一个AXI-IP核

- 一步一步学ZedBoard & Zynq(四):基于AXI Lite 总线的从设备IP设计

- 一步一步学ZedBoard & Zynq(四):基于AXI Lite 总线的从设备IP设计

- 2017/09/25 关于cache和axi的一些想法

- ZYNQ使用AXI VDMA搭建图像通路

- Vivado下创建基于AXI-Lite的用户IP核

- Vivado中AXI IP核的创建和读写逻辑分析

- AXI4-Stream协议的信号以及Xilinx提供的从AXI到AXI-Stream转换的IP核区别

- AXI协议整理

- AXI DMA (1)

- zc702-自定义AXI-IP核实验

- PAT|中国大学MOOC-翁恺-C语言程序设计习题集17-20

- Using CMake to Build Qt Projects

- Zedboard-关于Zedboard的FSBL的一些问题讨论

- -XX:+TraceClassLoading在eclipse中的用法

- Zedboard-ZYNQ架构整理

- Zedboard-一些常见的IP核整理(AXI-Interconnect和AXI VDMA)

- android报错:Class resolved by unexpected DEX

- [LeetCode] Two Sum

- Zedboard-Ubuntu12.04内核编译

- 基于AWS的电子商务网站架构——Web前端

- iOS 委托代理delegate设计模式

- bzoj3774: 最优选择

- Web.xml详解

- 面向对象第二课,类和对象的关系