iMX6 IPU 之CM .

来源:互联网 发布:淘宝购物流程步骤图 编辑:程序博客网 时间:2024/05/02 04:23

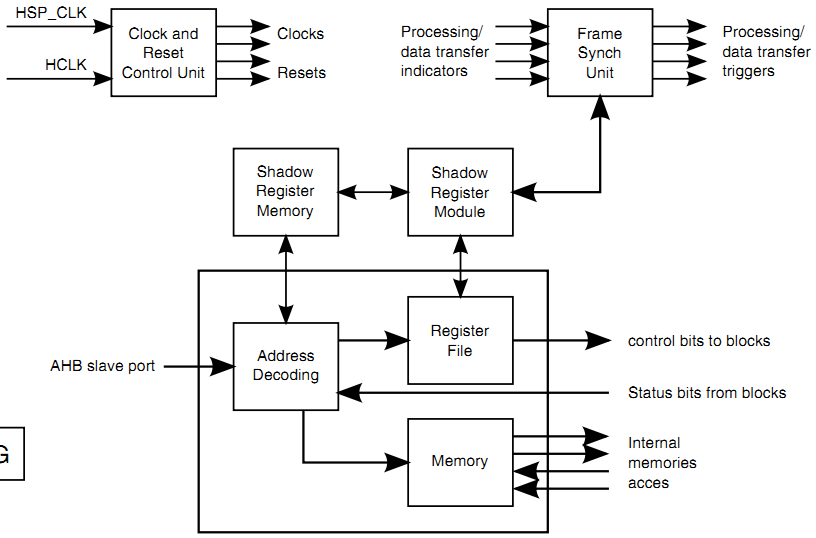

The CM consists of the Frame Synchronization Unit (FSU), the Interrupt Generator (IG), the General Configuration Registers (GCR), the Clock and Reset Control Unit (CRCU) and the Shadow Registers Block (SRM).

部分CM模块框图

CM模块为IPU控制部分的逻辑核心,他负责协调IPU内部各子模块工作(FSU),IPU内部存储单元控制,时钟电源控制等,他是IPU与ARM交互的控制中转枢纽,包括下面的八个子模块。AHB总线访问各模块内部配置寄存器,IPU内部RAM。各模块复位时钟控制,数据传输触发。

一、Frame Synchronization Unit

FSU负责各模块的工作协调,和实现开启数据处理后ARM零干预的执行机构。帧同步控制流程如下:

ARM配置所有相关参数寄存器,完成IPU必要的初始化动作。

使能FSU与IPU即将投入使用的相关模块。

FSU等待由ARM或模块发出的NEW_FRM_RDY等触发信号。

同步协调各模块工作--DMA操作,监控,状态切换,根据状态决定是否开始流水处理或者进入暂停等待。

用户终止或操作完成

IPU内部需要协调5种数据流。根据IPU即图像处理单元,为什么会有同步问题?应该主要因为我们需要控制高速与低速设备间同步问题,当单一模块完成数据处理后怎么开启下一模块实现流水线处理。

FSU需要肩负双显示输出同步控制,双buffer轮转控制。下面框图的每一条箭头表示一次数据传输,那么相应的需要进行同步控制。

双输出数据流程

数据传输启动顺序为:Camera完成后启动IC IC完成后启动DP,此外CM还得控制数据流写向正确的DI(LCD)。

Snooping

Automatic Window Refresh

Synchronization with A Video/Graphics source

二、Shadow Registers Module

引入该模块可进一步加速双显示切换效率。毕竟AHB总线也不是你一个人的。

三Interrupt Generator

四、SDMA event generator

五、General Configuration Registers

六、Memory Access Unit

七、SISG - Still Image Synchronization Generator

八、Clock Change procedureLow

九、Power Modes - Stop, PG and LPSR modes

the FSU automatically toggles the DMA_CH_CUR_BUF_# to point on the correct buffer to be used by the channel

- iMX6 IPU 之CM .

- iMX6 IPU之DP .

- iMX53 IPU图解之CM

- iMX53 IPU图解之IDMAC

- iMX53 IPU图解之DP

- imx6之kernel移植

- imx6之camera mipi

- CM之过程总览

- iMX53 IPU 图解之概述篇

- cm

- CM

- Android之build.prop imx6

- 3-6q环视之显示,ipu的注册

- 基于imx6.linux理解之v4l2

- IMX6之SPI接口驱动测试

- IMX6之openwrt设置samba共享

- OSGI CM之ManagedService的使用

- OSGI CM之ManagedServiceFactory的使用

- 平衡二叉树(AVLTree)

- 前端部分开发工具-个人收藏

- MyEclipse 2015最新版下载

- 面试题:两个无序数组合并成一个有序数组

- linux软件包管理 rpm yum dpkg apt-get

- iMX6 IPU 之CM .

- shared_pointer

- OpenGL ES 2.0 编程三步曲

- 《跨界杂谈》企业商业模式(四):弹性

- android动态加载及插件化开发探讨

- python subprocess

- 附加属性案例

- 习惯的力量

- copy,retain,weak,strong等的总结