《Xilinx可编程逻辑器件设计与开发(基础篇)》连载13:Spartan-6的BRAM(Block RAM)模块

来源:互联网 发布:如何分析大数据 编辑:程序博客网 时间:2024/05/24 06:37

2.1.4 BRAM(Block RAM)模块

Spartan-6中的BRAM存储18Kbit数据,能配置成两个独立的9Kbit BRAM或者一个18Kbit BRAM。每个RAM可以通过两个端口寻址,也可以配置成单口RAM。BRAM包含输出寄存器以增加流水线性能。BRAM 在器件中按列排列,其数量取决于Spartan-6 器件的容量。

BRAM 的功能介绍如下。

Spartan-6的BRAM同其他Xilinx FPGA BRAM类似,支持写/读同步操作,两个端口对称且完全独立,共享数据,每个端口根据需要可以改变其位宽和深度。存储器内容可在配置比特流时进行清除或设置。

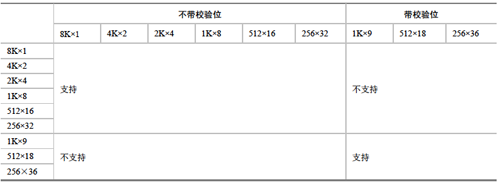

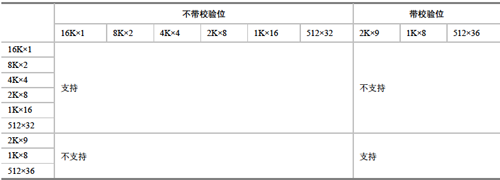

Spartan-6中的BRAM配置十分灵活,如表2-10至表2-13所示。BRAM配置为完全双口模式时,每个端口都支持写或读操作;BRAM配置为简单双端口模式时,A口只支持写操作,B口只支持读操作。

表2-10 9Kbit BRAM的简单双口配置

表2-11 9Kbit BRAM的全双口配置

表2-12 18Kbit BRAM的简单双口配置

表2-13 18Kbit BRAM 的全双口配置

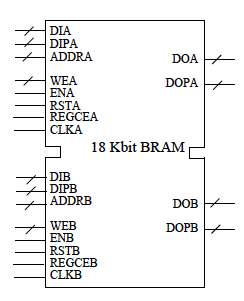

每个BRAM可以配置成完全的双口RAM,有18Kbit的存储空间和两个完全独立的访问口:A口和B 口,结构对称,A 口B 口有独立的地址、数据输入、数据输出、时钟、时钟允许和写允许信号。数据可以写入其中的一个口或者两个口,也可以从一个或者两个口读出,如图2-30所示。

需要注意的是,当两个端口同时对同一个地址操作时,由于双端口RAM 内部没有专门的监控逻辑,因此需要用户监控,以免冲突。两个端口同时对同一个地址的操作不会损坏该物理空间。读写的详细时序请参考用户指南。

每个9Kbit 或者18Kbit BRAM 都可配置成简单双口RAM,区别在于A 口是写操作,B口是读操作,读写都可同时发生。

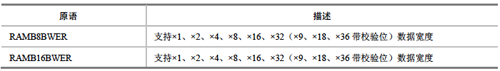

全双口RAM 和简单双口RAM 的原语见表2-14 所示,可以在HDL 代码中直接例化。

表2-14 Spartan-6 BRAM 的原语

- BRAM(Block

- RAM)模块

- Spartan-6

- Xilinx可编程逻辑器件设计与开发

- 《Xilinx可编程逻辑器件设计与开发(基础篇)》连载13:Spartan-6的BRAM(Block RAM)模块

- 《Xilinx可编程逻辑器件设计与开发(基础篇)》连载49:Spartan-6的PicoBlaze性能

- 《Xilinx可编程逻辑器件设计与开发(基础篇)》连载21:Spartan-6的时钟资源

- 《Xilinx可编程逻辑器件设计与开发(基础篇)》连载21:Spartan-6的时钟资源

- Xilinx可编程逻辑器件设计与开发(基础篇)

- 可编程逻辑器件基础

- 可编程逻辑器件基础

- 自己动手写处理器之第二阶段(1)——可编程逻辑器件与PLD电路设计流程

- 数字电子技术复习(六)——存储器与可编程逻辑器件

- 基于VHDL的复杂可编程逻辑器件(CPLD)应用技术--绪论

- xilinx Spartan 6 DFT 设计笔记

- 针对BGA封装可编程逻辑器件设计的低成本布板技术

- 基于Xilinx Spartan 3E-1200开发板的多功能秒表设计

- 可编程逻辑器件网址 altera

- 复杂可编程逻辑器件CPLD

- 可编程逻辑器件的发展历程及概述

- FPGA基础知识3(xilinx CLB资源详解--slice、分布式RAM和Block ram)

- FPGA基础知识3(xilinx CLB资源详解--slice、分布式RAM和Block ram)

- java 学习银行调度学习笔记

- 什么是seo

- Datatable导出到Execl中

- C语言数据定义长度 16位、32位、64位

- document.documentElement与document.body

- 《Xilinx可编程逻辑器件设计与开发(基础篇)》连载13:Spartan-6的BRAM(Block RAM)模块

- HDOJ-5446 Clarke and problem(DP)

- SQL Server

- c指针加减值得问题

- 一键清除Centos iptables 所有规则

- Call to undefined function curl_init()解决方法

- Hadoop分布式存储系统HDFS

- 黑马程序员---Java面向对象(上)

- 给一组数,只有两个数只出现了一次,其他所有数都是成对出现的。怎么找出这两个数。