Xilinx RocketIO模块的介绍

来源:互联网 发布:nba球员生涯数据 编辑:程序博客网 时间:2024/04/29 22:50

摘要: 在高速电路系统设计中,差分串行通信方式正在取代并行总线方式,以满足系统对高带宽数据通信的需求。RocketIO是Virtex2 Pro以上系列FPGA中集成的专用高速串行数据收发模块,可用于实现吉比特的数据传输,适用于多种高速数据传输协议。依据实际工程应用需求,提出了基于RocketIO的高速串行数据传输系统解决方案,实现了每通道2.5 Gb/s的传输速度。最后介绍了RocketIO在Aurora和PCI Express协议实现中的应用,并总结了高速通信系统的共性特征。

引言

随着电子系统对速度以及精度要求的提高,高速串行数据通信模式正在逐步取代传统的并行总线式结构。并行总线结构由于其固有的缺点,在速度上的提升空间已经很小。

① 并行总线在印制电路板上要占用大量的空间,在电路系统日益小型化的今天给系统的设计带来很大困难。如PATA66以上的PATA排线数量达到了80根,使得电路板的布线极为困难。

② 并行总线由于在布线时很难保证每条线路长度与电气特征一致,导致信号到达时间不同,在较高的工作频率下很难实现完全同步,以致出现信号偏移。这使接收器难以确定采样时间,容易造成数据错误。

③ 由于寄生电容的影响,在并行的两条数据线中容易产生串扰,甚至改变信号原有真实电平。采用地线进行屏蔽可以在一定程度上消除串扰,但同时也造成总线线路数目的急剧增加。

④ 并行总线参考电平为地电平,容易受噪声干扰。同时由于在总线上“0”、“1”分布不均匀,在信号收发器之间易造成直流偏置,造成信号噪声容限降低。

相比而言,高速串行总线采用差分对的形式,并且在发送端与接收端之间采用点对点的连接结构。差分信号经过编码,消除信号序列中直流分量,从而可以提高噪声容限。同时,在信号序列中插入时钟信息,信号中携带时钟,解决了信号偏移问题。

在嵌入式应用方面,主流的FPGA中都已对差分信号提供了硬件支持,如Xilinx公司推出的Virtex系列FPGA中,相邻的两个I/O口都以差分信号对形式出现。从Virtex2 Pro系列开始,更是在片上集成了固化的RocketIO模块,以提供高超高速的串行通信支持。本文将从工程应用的角度出发介绍RocketIO的相关特征,并探讨其在高速数据传输中的应用。

1 RocketIO

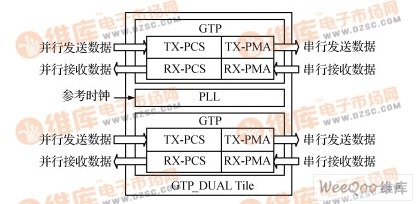

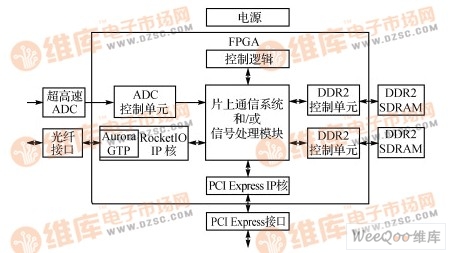

RocketIO收发器是在Virtex2 Pro以上系列FPGA中集成的专用串行通信模块,在使用时不占用FPGA其他逻辑与片上存储资源。在Virtex5 LXT和SXT系列FPGA中,RocketIO称为GTP,每两个GTP共用一个PLL,组成一个GTP_Dual。其结构框图如图1所示。

图1 GTP_Dual Tile结构框图

每一个RocketIO收发器均具有如下特征:

◆ 具有可配置终端、电压摆幅与耦合的电流模逻辑串行驱动或缓冲器。

◆ 可编程发送预加重和接收均衡,以实现最优信号完整性。

◆ 100 Mb/s~3 Gb/s的线速范围,线速在100 Mb/s~500 Mb/s区间时具有可选的5倍过采样功能。

◆ 可选的嵌入式PCS功能,例如8位/10位编码、逗号对齐、通道绑定以及时钟校正。

◆ 最小化的确定性数据通道延迟。

◆ 对PCI Express、SATA、光纤传输等协议的支持。

从应用上讲,RocketIO处于数据传输协议的物理层,用以实现最基本的数据通信环境。其主要功能可以概括为:将输入的并行数据经过编码,转化为高速的差分串行信号。在实际应用中,输入时钟、PLL参数设置以及PCB线路的设计与布局是影响数据传输效果的最重要因素。

1.1 输入时钟

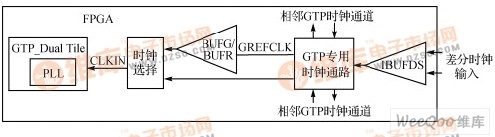

RocketIO有三种时钟输入方式:专用差分时钟、共享邻近GTP_Dual的时钟、以及使用FPGA内部时钟。Rocket I/O GTP时钟输入方式如图2 所示。

图2 Rocket I/O GTP时钟输入方式

使用专用差分时钟时,差分的时钟信号通过输入差分缓冲器变为单端时钟,输入到GTP_Dual Tile中的PLL,当使用的时钟源精度满足要求时具有最优的时钟稳定性。

从相邻GTP_Dual Tile获得时钟时需要使用GTP专用的时钟通路,但此时GTP_Dual与提供时钟的GTP_Dual Tile间隔的GTP_Dual Tile个数不能超过两个,即每对差分输入时钟最多可驱动7个GTP_Dual Tile。

相比于上述两种时钟输入方式,从FPGA内部获得时钟时钟精度最差。这是因为,FPGA内部使用的时钟经过逻辑电路以及BUFG或BUFR缓冲后,会引入较大的时间抖动。但由于在FPGA内部可以灵活变换参考时钟频率,因此在速度与精度要求不太高的场合可采用FPGA内部时钟。经实验验证,对于误码率要求在1‰以下的应用,从FPGA内部获得的时钟信号可以满足要求。

1.2 PLL参数设置

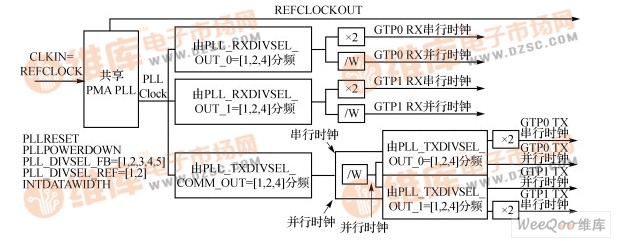

时钟信号输入到GTP_Dual Tile内部后还需要经过PLL的进一步处理才能使用。PLL可向两个RocketIO提供相互独立的各种时钟信号。PLL内部时钟变换结构如图3所示。

图3 PLL内部时钟变换结构

需要注意的是,由于此PLL可用参数(PLL_DIVSEL_FB = [1,2,3,4,5], PLL_DIVSEL_REF = [1,2])有限,为获得高速串行通信所需频率,输入参考时钟CLKIN仅可在有限范围内选择。因此,参考时钟需通过专用的具有相应频率的晶振提供或在FPGA内部经DCM或PLL变换获得。

1.3 PCB设计

RocketIO产生的高速串行信号速度在1 GHz以上时,已经进入微波范围。因此在使用时,其PCB电路的制作也是影响信号传输效果的重要因素。

RocketIO的供电必须由专用的电源管理模块提供,不能与其他模块电源共享,以减少噪声引入。即使GTP中同一种电源的不同引脚之间也需要通过滤波电路进行隔离,以减少相互之间的影响。为平衡GTP_Dual Tile的负载,只使用其中的一个GTP时,两个GTP的供电应以同样策略进行处理。

在布线时,高速差分对走线应当有最高的优先级,以保证其电气特性满足微带线或带状线的要求。走线应当尽量直、短并具有最少的信号层变化。为减少干扰信号的影响,高速线应尽量远离其他有可能会带来噪声的信号线,同时信号线拐角采用45°而避免使用直角。为保证信号的完整性,高速差分信号线的参考平面须保持连续,并尽量以地平面为参考,否则其阻抗特性会发生急剧变化,导致信号的反射增强。

2 RocketIO在高速信号传输中的应用

在多种高速数据处理场合都需要对数据进行高速收发。以超高速信号采集系统为例,当采用ADC08D1500采集芯片时,最高可以实现单通道3 Gsps的超高速采样率,数据精度为8位。这时就需要具有足够高传输速率的信号传输机制对信号进行转发。若实现机内通信,可采用PCI Express传输协议;若实现系统间通信,则可使用光纤通信协议或千兆以太网协议。在工程中,上述协议都可通过专用的芯片来实现,但也使得系统变得复杂,同时使电路板的设计空间紧张。而RocketIO对多种高速传输协议的支持,可以使得PCI Express协议、光纤传输协议或千兆以太网协议在同一片FPGA内实现,提高了系统的集成度,并使得信号的处理机制更加灵活。在本文的设计中,采用了PCI Express传输协议来实现机内通信,采用Aurora光纤传输协议来实现系统间通信。系统结构如图4所示。

图4 超高速采集系统框图

2.1 Aurora协议

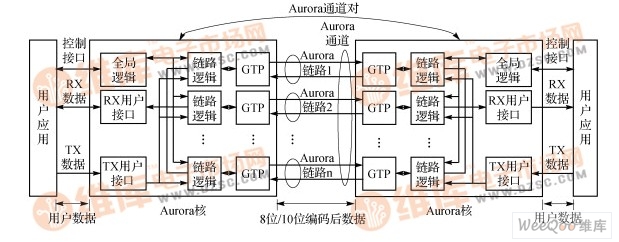

Aurora协议是一种可配置的、简便的数据链路层协议,可以通过使用一条或多条高速串行通道实现点对点的数据传输。Aurora协议可为私有上层协议或标准上层协议提供透明接口的串行互联协议,允许任何数据分组通过Aurora协议封装,并在芯片间、电路板间甚至机箱之间传输。Xilinx还开发了实现该协议的Aurora IP核,当使用Virtex5 FPGA提供的RocketIO时,Aurora可实现每个物理通道500 Mb/s到3.75 Mb/s的传输速率。Aurora可将1~16个物理通道绑定在一起,形成一个由16个通道绑定而成的虚拟链路,提供最高60 Gb/s的传输波特率[1]。其结构如图5所示。

图5 Aurora核结构

Aurora核可以帧模式或流模式传输数据[4]。Aurora的帧可以是任意大小,并可以在任意时刻被中断。有效数据之间被自动以空闲(idles)序列信号填充,以维持通道的锁定。帧模式下有可选的数据流控制信号,以降低接收数据速率,或传送简短而优先级高的信息。流模式在Aurora核中以一个无结尾的帧方式实现。在数据传输的间隙补以空闲序列信号。

2.2 PCI Express协议

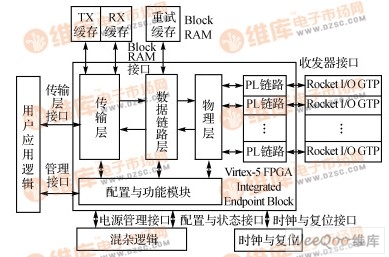

PCI Express是PCI、PCIX协议的下一代协议,是一种广泛适用于计算和通信平台的高性能通用互联结构。同Aurora协议相似,PCI Express协议采用点到点的串行链接,单通道可实现2.5 Gb/s的传输速率,最高可使用16个通道实现40 Gb/s的高速通信。Xilinx公司开发的集成的PCIE IP核(Integrated Endpoint Block)可实现最高8个RocketIO通道的绑定,以此为物理层基础实现20 Gb/s的传输速率。PCI Express协议包含传输层、数据链路层和物理层,其在FPGA上基于RocketIO实现的结构框架如图6所示。

图6 Xilinx PCIE IP核结构框图

2.3 高速信号传输系统的共性

RocketIO可应用于多种高速数据处理应用的场合,这是由于高速信号传输系统结构都可以概括为三个组成部分,并且传输协议分层实现的方式使得系统协议与硬件系统之间具有一定的独立性。

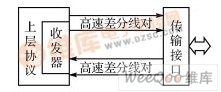

图7 高速信号传输系统框架图

高速信号传输系统的实现方式多种多样,但一般均由上层协议、高速收发器以及传输接口组成。其结构框架如图7所示。

上层协议:根据不同的任务需要,为实现高速信号传输制定的传输协议多种多样,包含的层数也不同。如PCI Express协议具有物理层、数据链路层以及传输层,Aurora协议具有物理层和数据链路层,10 Gb/s以太网协议(XAUI)包含物理层和数据链路层。用户程序可使用这些传输协议实现数据的收发。

高速收发器:高速收发器是所有传输协议都必须具备的物理层,是实现高速信号传输的基础。一般实现串并转换、时钟数据恢复、线路编码、线路绑定等功能,可为多种上层协议提供硬件支持。Xilinx公司推出的RocketIO与Altera公司推出的Rapid IO等都可看作高速收发器。

传输接口:在高速的信号传输系统中传输接口与高速收发器之间通过差分线连接,可实现全双工的双向传输。接口形式与具体应用相关,如实现PCI Express传输协议的PCIE接口、实现光线传输协议的光线接口以及实现高速以太网通信的网络接口等。

其中相同的高速收发器可以应用于使用不同传输协议的系统中,所连接的接口根据不同应用而有不同形式。如RocketIO既可用于Aurora光纤通信协议,也可用于PCI Express协议。而在Aurora协议中,RocketIO与光纤接口相连,在PCI Express协议中,RocketIO与PCIE接口相连。

结语

综上所述,RocketIO通过提供高速的串并转换、时钟与复位管理、线路编解码等功能,为实现高速的串行数据传输提供了良好的物理层基础。RocketIO对多种高速传输协议的支持使得其在嵌入式系统中得到了广泛的应用,也使得用户在选择使用成熟的IP核之外,可以根据实际需要利用RocketIO开发专用模块,实现高效、稳定的数据传输。

- Xilinx RocketIO模块的介绍

- VDMA IP的GUI配置介绍【Xilinx-VDMA模块学习】

- RocketIO

- Xilinx Select IO的介绍

- -01- VDMA IP的GUI配置介绍【Xilinx-VDMA模块学习】

- xilinx 的socket CAN驱动介绍

- Xilinx Arm 8的内容介绍

- Xilinx System Generator模块中各个常见选项的含义

- -02-Xilinx的SerDes接口介绍【Xilinx-LVDS读写功能实现】

- FFT的分析和XILINX fft核的介绍

- Xilinx FFT IP core V9.0的介绍和使用

- Xilinx—Zynq架构介绍

- Xilinx 7系列FPGA介绍

- 模块的介绍

- QT模块的介绍

- 兼容xilinx公司开发板设计--基于FMC接口的DSP TMS320C6455子卡模块

- 兼容xilinx公司开发板设计--基于FMC接口的DSP TMS320C6455子卡模块

- 对于rocketio和rapidio有模糊认识的可以参考以下文章

- 此篇为上一批连接数据库的注释①

- Java: 分页Paging的实现思路和Demo

- [已解决]亿图 Edraw 导出pdf 显示乱码的问题

- 第一篇博客

- Android公共技术点之一-Java注解

- Xilinx RocketIO模块的介绍

- [HTML/CSS]布局学习笔记-CSS网页平滑移动

- 素材采集 良心题解

- HTML学习小记3

- 自定义View 放在Dialog后点击事件无效

- Eclipse在异常关闭后,启动闪退的解决办法

- Spring-AOP-春天的故事3

- Andriod系统中关于BroadcastReceiver的说法正确的是?

- 万物皆对象,对象皆有类——另一种方式理解Object类,Class类