LVDS信号介绍及PCB设计

来源:互联网 发布:手机数据能删除吗 编辑:程序博客网 时间:2024/04/29 17:03

原文地址:http://www.cnblogs.com/hong-jing/p/5140666.html

收藏学习!!!

一.LVDS简介

1.1、LVDS信号介绍

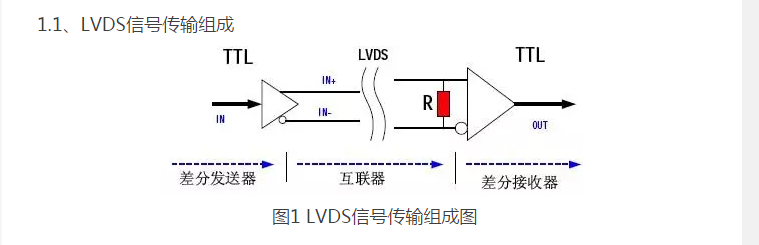

LVDS:Low Voltage Differential Signaling,低电压差分信号。LVDS传输支持速率一般在155Mbps(大约为77MHZ)以上。LVDS是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。IEEE在两个标准中对LVDS信号进行了定义。ANSI/TIA/EIA-644中,推荐最大速率为655Mbps,理论极限速率为1.923Mbps。LVDS信号传输一般由三部分组成:差分信号发送器,差分信号互联器,差分信号接收器。差分信号发送器:将非平衡传输的TTL信号转换成平衡传输的LVDS信号。通常由一个IC来完成,如:DS90C031;差分信号接收器:将平衡传输的LVDS信号转换成非平衡传输的TTL信号。通常由一个IC来完成,如:DS90C032;差分信号互联器:包括联接线(电缆或者PCB走线),终端匹配电阻。按照IEEE规定,电阻为100欧。我们通常选择为100,120欧。

1.2、LVDS信号电平特性

LVDS物理接口使用1.2V偏置电压作为基准,提供大约400mV摆幅。LVDS驱动器由一个驱动差分线对的电流源组成(通常电流为3.5mA),LVDS接收器具有很高的输入阻抗,因此驱动器输出的电流大部分都流过100Ω 的匹配电阻,并在接收器的输入端产生大约350mV 的电压。电流源为恒流特性,终端电阻在100――120欧姆之间,则电压摆动幅度为:3.5mA * 100 = 350mV ;3.5mA * 120 = 420mV.

由逻辑“0”电平变化到逻辑“1”电平是需要时间的。由于LVDS信号物理电平变化在0。85――1。55V之间,其由逻辑“0”电平到逻辑“1”电平变化的时间比TTL电平要快得多,所以LVDS更适合用来传输高速变化信号。其低压特点,功耗也低。采用低压技术适应高速变化信号,在微电子设计中的例子很多,如:FPGA芯片的内核供电电压为2。5V或1.8V;PC机的CPU内核电压,PIII800EB为1.8V;数据传输领域中很多功能芯片都采用低电压技术。

1.3、差分信号抗噪特性

从差分信号传输线路上可以看出,若是理想状况,线路没有干扰时,在发送侧,可以形象理解为:

IN=IN+-IN-

在接收侧,可以理解为:

IN+-IN-=OUT

所以:

OUT=IN

在实际线路传输中,线路存在干扰,并且同时出现在差分线对上,

在发送侧,仍然是:

IN=IN+-IN-

线路传输干扰同时存在于差分对上,假设干扰为q,则接收则:

(IN++q)-(IN--q)=IN+-IN-=OUT

所以:

OUT=IN

噪声被抑止掉。

上述可以形象理解差分方式抑止噪声的能力。在实际芯片中,是在噪声容限内,采用“比较”及“量化”来处理的。

LVDS接收器可以承受至少±1V的驱动器与接收器之间的地的电压变化。由于LVDS驱动器典型的偏置电压为+1.2V,地的电压变化、驱动器偏置电压以及轻度耦合到的噪声之和,在接收器的输入端相对于接收器的地是共模电压。这个共模范围是:+0.2V~+2.2V。建议接收器的输入电压范围为:0V~+2.4V。

抑止共模噪声是DS(差分信号)的共同特性,如RS485,RS422电平,采用差分平衡传输,由于其电平幅度大,更不容易受干扰,适合工业现场不太恶劣环境下通讯。

二.LVDS信号的PCB设计:

1、LVDS信号的工作原理和特点

对于高速电路,尤其是高速数据总线,常用的器件一般有:ECL、BTL、GTL和GTL+等。这些器件的工艺成熟,应用也较为广泛,但都存在一个共同的缺点,即功耗大。

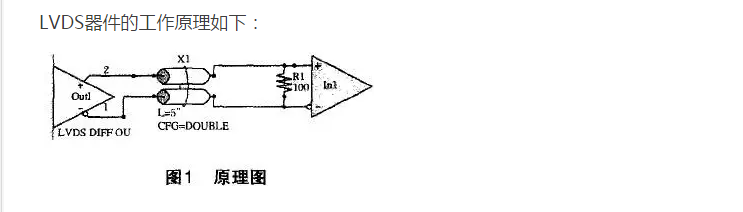

新兴的CM0S工艺的低压差分信号(Low Voltage Differential Signal,简称LVDS)器件给了我们另一种选择。LVDS低压差分信号,最早由美国国家半导体公司(National Semiconductor)提出的一种高速串行信号传输电平,由于它传输速度快,功耗低,抗干扰能力强,传输距离远,易于匹配等优点,迅速得到诸多芯片制造厂商和应用商的青睐,并通过TIA/EIA (Telecommunication Industry Association/Electronic Industries Association)的确认,成为该组织的标准(ANSI/TIA/EIA-644 standard)。LVDS信号被广泛应用于计算机、通信以及消费电子领域,并被以PCI-Express为代表的第三代I/O标准中采用。LVDS器件的工作原理如下:

如图1所示,其中发送端是一个3.5mA的电流源,产生的3.5mA的电流通过差分线中的一路到接收端。由于接收端对于直流表现为高阻,电流通过接收端的100Ω的匹配电阻产生350mV的电压,同时电流经过差分线的另一路流回发送端。当发送端进行状态变化时,通过改变流经100Ω电阻的电流方向产生有效的'0'和'1' 态。

LVDS的特点是电流驱动模式,低电压摆幅350mV可以提供更高的信号传输率,使用差分传输的方式,输入信号只与2个信号的差值有关,可将共模干扰抑制掉,可以使信号的噪声和EMI都减少。综上所述,LVDS有以下主要特点:

1.低的输出电压摆幅(350mV);

2.差分特征是磁干扰相互抵消,消除共模噪声,减少EMI;

3.传输速度快,功耗低,抗干扰能力强,传输距离远,易于匹配等优点。

二、LVDS信号在PCB上的设计

由LVDS信号的工作原理及特点可以看出:LVDS信号不仅是差分信号,而且还是高速数字信号;因此LVDS传输媒质不管使用的是PCB线对还是电缆,都必须采取措施防止信号在媒质终端发生反射,同时应减少电磁干扰以保证信号的完整性。只要我们在布线时考虑到以上这些要素,设计高速差分线路板并不很困难。下面将简要介绍LVDS信号在PCB 上的设计要点:

1.布成多层板。有LVDS信号的印制板一般都要布成多层板。由于LVDS信号属于高速信号,与其相邻的层应为地层,对LVDS信号进行屏蔽防止干扰。另外密度不是很大的板子,在物理空间条件允许的情况下,最好将LVDS信号与其它信号分别放在不同的层。例如,对于四层板,通常可以按以下进行布层:LVDS信号层、地层、电源层、其它信号层。

2.LVDS信号阻抗计算与控制。

LVDS信号的电压摆幅只有350 mV,适于电流驱动的差分信号方式工作。为了确保信号在传输线当中传播时不受反射信号的影响,LVDS信号要求传输线阻抗受控,通常差分阻抗为(100±10)Ω。阻抗控制的好坏直接影响信号完整性及延迟。如何对其进行阻抗控制呢?

①、确定走线模式、参数及阻抗计算。LVDS分外层微带线差分模式和内层带状线差分模式两种,分别如图2、图3所示。通过合理设置参数,阻抗可利用相关阻抗计算软件(如POLAR-SI6000、CADENCE的ALLEGRO)计算也可利用阻抗计算公式计算。图2、图3为POLAR-SI6000阻抗计算软件计算阻抗值。

阻抗计算公式计算阻抗。以上微带线和带状线种方式阻抗计算公式分别为:

(i)微带线(microstrip)

Z={87/[sqrt(εr+1.41)]}ln[5.98H/(0.8W+T)]

其中,W为线宽,T为走线的铜皮厚度,H为走到参考平面的距离,εr是PCB板材质的介电常数(dielectric Constant)。此公式必须在0.1<(W/H)<2.0及1<(εr)<15的情况才能应用。

(ii)带状线(stripline)

Z=[60/sqrt(εr)]ln{4H/[0.67π(T+0.8W)]}

其中,H为两参考平面的距离,并且走线位于参考平面的中间。此公式适应于双线,线间距与抗成正比,必须在W/H<0.35及T/H<0.25的情况才应用。

由上面两公式可以看出,虽然其计算公式各不同,但阻抗值均与绝缘层厚度成正比,与介电常数、线的厚度及宽度成反比。

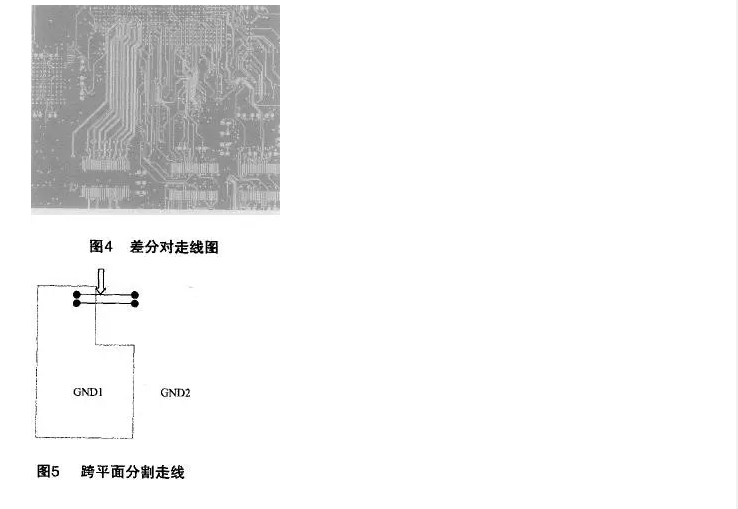

②、走平行等距线(如图4)。确定走线线宽及间距,在走线时要严格按照计算出的线宽和间距,两线间距要一直保持不变,也就是要保持平行(如图4示)。平行的方式有两种: 一种为两条线走在同一线层(side-by-side),另一种为两条线走在上下相两层(over-under)。一般尽量避免使用后者即层间差分信号,因为在PCB板的实际加工过程中,由于层叠之间的层压对准精度大大低于同层蚀刻精度,以及层压过程中的介质流失,不能保证差分线的间距等于层间介质厚度,会造成层间差分对的差分阻抗变化。困此建议尽量使用同层内的差分。

3.紧耦合原则。

在计算线宽和间距时最好遵守紧耦合的原则,也就是差分对线间距小于或等于线宽。当两条差分信号线距离很近时,电流传输方向相反,其磁场相互抵消,电场相互耦合,电磁辐射也要小得多。

4.走短线、直线。

为确保信号的质量,LVDS差分对走线应该尽可能地短而直,减少布线中的过孔数,避免差分对布线太长,出现太多的拐弯,拐弯处尽量用45°或弧线,避免90°拐弯。

5.不同差分线对间处理。

LVDS对走线方式的选择没有限制,微带线和带状线均可,但是必须注意要有良好的参考平面。对不同差分线之间的间距要求间隔不能太小,至少应大于3~5倍差分线间距。必要时在不同差分线对之间加地孔隔离以防止相互问的串扰。

6.LVDS信号远离其它信号。

对LVDS信号和其它信号比如TTL信号,最好使用不同的走线层,如果因为设计限制必须使用同一层走线,LVDS和TTL的距离应该足够远,至少应大于3~5倍差分线间距。

7.LVDS差分信号不可以跨平面分割。

尽管两根差分信号互为回流路径,跨分割不会割断信号的回流,但是跨分割部分的传输线会因为缺少参考平面而导致阻抗的不连续(如图5箭头处所示,其中GND1、GND2为LVDS相邻的地平面)。

8.接收端的匹配电阻的布局。

对接收端的匹配电阻到接收管脚的距离要尽量靠近。如图5的矩形处为接收端的匹配电阻。

9.匹配电阻的精度要求。

对于点到点的拓扑,走线的阻抗通常控制在100Ω,但匹配电阻可以根据实际的情况进行调整。电阻的精度最好是1%~2%。因为根据经验,10%的阻抗不匹配就会产生5%的反射。

三、LVDS信号PCB设计实例

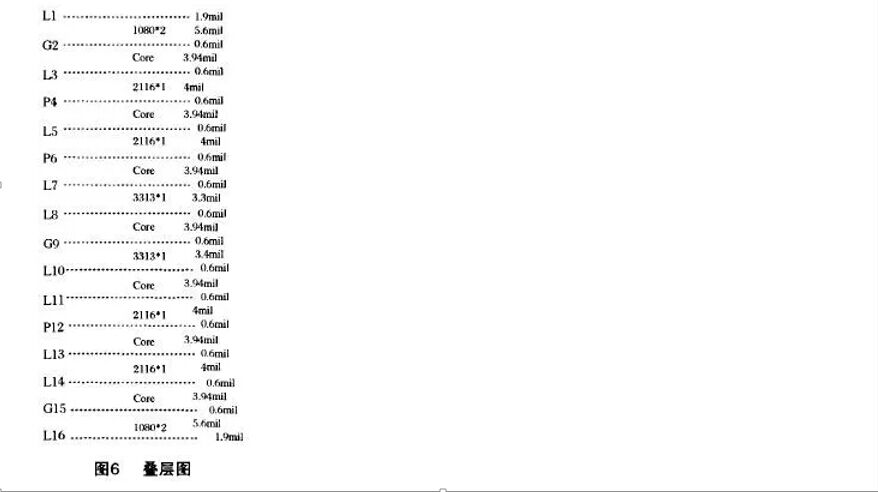

根据以上处理原则,简单介绍一块LVDS信号PCB设计实例,此板为16层多层印制板,叠层与板材(FR-4板材)关系如图6。

LVDS信号分别走在L1和L16层,L1的屏蔽层为G2,L16屏蔽层为G15(其中G2、G15是一完整的地平面),这样不但可以减少过孔数、线短,而且每个LVDS信号层都有完整的参考地平面相邻。

利用POLAR-SI6000计算表面微带差分走线:线宽6mils,线间距为6mils,阻抗理论计算值为99.1Ω。在生产过程中通过严格控制各种参数,利用CITS500S阻抗测试仪测试附连板的阻抗值范围为(95.6~106.8)Ω,完全符合阻抗控制要求。

- LVDS信号介绍及PCB设计

- LVDS信号介绍

- LVDS(低电压差分信号)介绍

- LVDS 信号

- 信号完整性:PCB设计中的信号完整性

- 带噪声的1KHz微弱信号采集系统设计仿真及制PCB板过程

- 混合信号PCB的分区设计

- 高速PCB电路板的信号完整性设计

- LVDS信号与TTL信号

- PCB设计步骤详细介绍

- EAGLE PCB设计软件介绍

- 信号处理系统PCB板设计(2008.10.06)

- 基于信号完整性分析的高速PCB设计

- 1600Mbps DDR3 高速信号仿真和PCB设计

- 1600Mbps DDR3 高速信号仿真和PCB设计 .

- PCB设计中的电源信号完整性的考虑

- 混合信号PCB设计中单点接地技术的研究

- 针对DDR2-800和DDR3的PCB信号完整性设计

- android点击空白地方隐藏软键盘

- ES Search APIs(持续更新)

- 对jQuery对象的理解

- Unity3D研究院之设置自动旋转屏幕默认旋转方向

- transient和volatile

- LVDS信号介绍及PCB设计

- Java中的instanceof关键字

- 多线程的join方法

- 排序算法总结

- Android手机 Fildder真机抓包

- Minimum Genetic Mutation

- 你很努力,但是表现却不好

- JDBC----使用Driver接口连接数据库

- ajax安全性问题