uda1341原理及驱动

来源:互联网 发布:电话布线使用网络 编辑:程序博客网 时间:2024/04/30 03:01

转自http://blog.csdn.net/bingqingsuimeng/article/details/8185628

现在主流的音频总线接口有IIS和AC97(Audio Codec)。

一。IIS是由sony和PILIPS公司共同推出的一套标准。

IIS有3--5根物理连线

IIsDI:串行数据输入

IISDO:串行数据输出

IISSCLK:为串行数据提供位时钟。IISSCLK=声道数*采样频率*采用位数。如:fs=44.1Khz 声道数位2.采样位数为16.则可以知道 IISCLK的具体数值。

IISLRCK:帧时钟,用于左右声道的切换,IISLRCK为高电平时表示正在传输的是左声道数据,为低时传输的是右声道数据,因此IISLRCK应正好与采样频率相等。(WS)

MCLK(也叫CDCLK编码解码时钟):由于IIS只是负责了数字音频信号的传输,要实现录音和放音还需要其他的芯片支持(如UDA1341),而CDCLK就能为芯片提供同步时钟信号。主要用于A/D.D/A时的采用时钟,一般为256fs或384fs

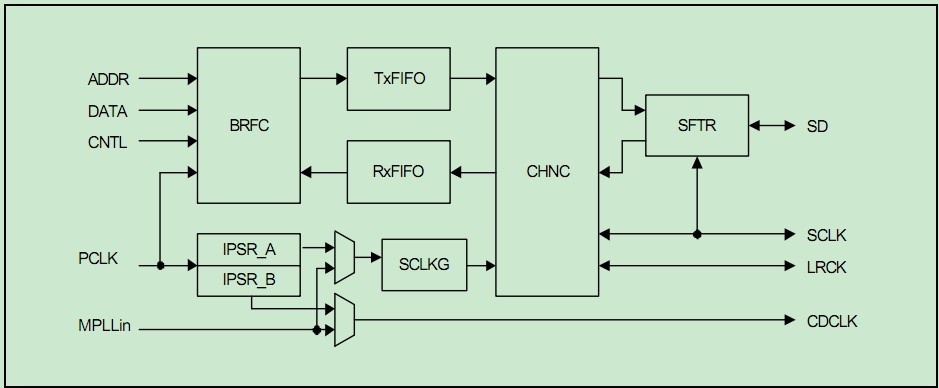

上面是IiS的总线控制器结构图

IPSR是连个5位的预分频器,其中IPSR_A用于产生II总线的主时钟,IPSR_B作用于外部音频芯片的时钟产生器。

FIFO:发送和接收缓冲区。

SCLKG:主IISCLK产生器

CHNC:通道产生器和状态机负责产生并控制IISCLK和IISLRCK.

SFTR:16位移位寄存器,主要负责对数据串并转换。

从上面可以看出设置fs的值相当重要。在2440中哟PCLK和MLLin可以提供IIS的时钟信号,我们这里选择了PCLK,经过分频之后可以得到IISCLK,IISLRCK,CDClK。(预分频A得到了IISCLK和IISLRCK,预分频B得到了CDCLK)一般A,B分频因子N是相等的。。而CDCLK=PCLK/(N+1).这里涉及到2440时钟的一些问题,还是先来回忆一下2440中的时钟结构:

1。在2440中有三种时钟。

FCLK is used by ARM920T.(If SLOW mode FCLK = input clock/divider ratio,If Normal mode (P, M & S value

FCLK = MPLL clock (Mpll))

HCLK is used for AHB bus, which is used by the ARM920T, the memory controller, the interrupt controller, the LCD

controller, the DMA and USB host block.

PCLK is used for APB bus, which is used by the peripherals such as WDT, IIS, I2C, PWM timer, MMC interface,

ADC, UART, GPIO, RTC and SPI

这里需要设置MPLLCON和IISPSR的值。假设fs=44.1Khz,CDCLK=384fs=16.9344Mhz,则N=3,MDIV=150,PDIV=5,SDIV=0,IISPSR=3<<5 | 3;

关于UDA1341:

UDA1341支持IIS总线数据格式,采用位元流转换技术进行信号处理,具有可编程增益放大器(PGA)和数字自动增益控制器(AGC)。 UDA1341对外提供两组音频信号输入接口,每组包括左右2个声道。由于IIS总线只处理音频数据,因此UDA1341还内置用于传输控制信号的L3总 线接口。L3接口相当于混音器控制接口,可以控制输入/输出音频信号的低音及音量大小等。

两组音频输入在UDA1341内部的处理存在很大的差别:第一组音频信号输入后巾帼一个0dB/6dB开关后采样送入数字混音器;第二组音频信号输入后先 经过可编程增益放大器(PGA),然后再进行采样,采样后的数据在经过自动增益控制器(AGC)送入数字混音器。硬件电路选用第二组输入音频信号,这样可 以通过软件的方法实现对系统输入音量大小的调节,显然,这可以用L3总线接口控制AGC来实现。

关于l3:

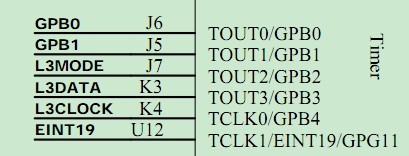

uda1341可以用L3总线接口调整pga,agc,vc等,来实现mixer。要通过L3来设置pga等,则需要先写相应的地址,然后在写相应的数 据。开发板用GPIO口来与L3接口相连:

S3C2410_GPB2 L3MODE

S3C2410_GPB3 L3CLOC1341_REG_STATUS

S3C2410_GPB4 L3CLOCK

L3地址时序:

首先将L3MODE,L3CLOCK置1,等待一段时间,然后重复以下步骤8次(对应与8位地址):将L3CLOCK拉低,置L3DATA为高或低(对应 与数据位是1还是0),等待一段时间后,拉高L3CLOCK。当8次结束后,将L3MODE,L3CLOCK恢复到1。

图:

L3数据时序(写):

L3MODE,L3CLOCK初始值都为1.重复以下步骤8次:

将L3CLOCK拉低,置L3DATA为高或低 (对应与数据位是1还是0),等待一段时间后,拉高L3CLOCK。当8次结束后,将L3MODE,L3CLOCK恢复到1。

图:

L3数据时序(读):

还不太懂。

L3的操作在uda1341_l3_address(),uda1341_l3_data()中实 现

2440与UDA1341相连除了使用IIS接口外,还需要使用L3总线来实现对声音的控制控制,同时2440还可以通过L3总线来设置UDA1341的寄存器,但是在2440中并没有L3总线接口,我们可以使用3个IO来模拟L3总线。在mini2440上我们可以看到

- uda1341原理及驱动

- uda1341原理及驱动

- uda1341原理及驱动

- uda1341原理及驱动

- fl2440 uda1341声卡驱动移植及madplay播放器移植

- UDA1341声卡驱动

- linux UDA1341 驱动注释

- 音频uda1341驱动移植

- 移植UDA1341音频芯片驱动

- UDA1341声卡驱动修改

- UDA1341 SSI音频驱动

- Linux——UDA1341驱动

- UDA1341声卡驱动 madplay 播放

- s3c2440 uda1341声卡驱动分析

- UDA1341声卡驱动放音测试程序

- UDA1341声卡驱动放音测试程序

- I2C硬件原理及驱动

- DMA原理及驱动开发

- 文件转成bety[] 图片转成 hex值

- 深入理解 Java 反射:Class (反射的入口)

- Ubuntu16.04源码编译mysql-5.6.26

- 一个pcap抓包分析code

- 篮球之背后运球

- uda1341原理及驱动

- 关于一些android数据库的创建

- 2017年初你绝对想尝试的25个新安卓库

- 判断字符串重排后是否相同(区分大小写)

- PAT甲级1010

- Android6.0新应用权限管理机制详解

- guava文件操作

- ASCII表

- 天瑞达安科技集团:Java工程师能从事什么工作,不单是程序员!!