07 初始化时钟

来源:互联网 发布:gnu与linux 编辑:程序博客网 时间:2024/06/06 04:37

1:s5pv210的时钟域

MSYS:(main system)主时钟域,包括CPU,DDR内存条,IROM和IRAM等

DSYS:(display system)显示时钟域,就是一般的和视频有关的就在这个时钟域中,如HDMI,TVENC等

PSYS:(peripheral system)外围时钟域,就是GPIO接口,I2C接口,UART接口等这些外围设备就在这个时钟域上。

注释:每个时钟域通过一条BRG(异步总线的桥梁)连接在一起。

2.晶振

常见的时钟的来源:

外部直接输入时钟信号,SoC有个引脚用来输入外部时钟信号,用的很少。

外部晶振+内部时钟发生器产生时钟,大部分低频单片机都是这么工作的。

外部晶振+内部时钟发生器+内部PLL产生高频时钟+内部分频器分频得到各种频率的时钟,210属于这种。

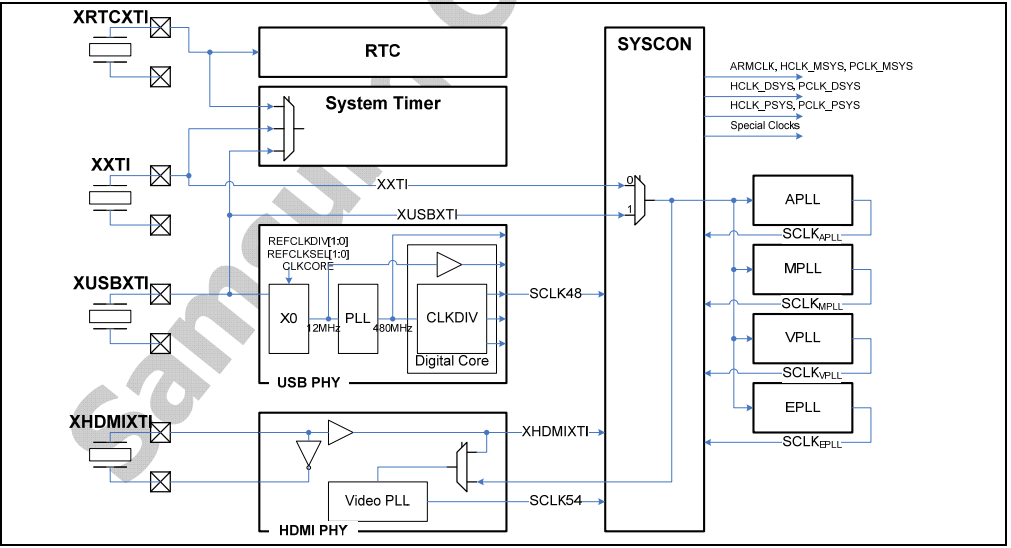

从上图可知:

s5pv210有4个晶振时钟,

XRTCXTI:提供32.768KHz,RTC 使用;XRTCXTI and XRTCXTO pins

XXTI:CMU and PLL使用这个时钟为APLL、MPLL、VPLL、EPLL提供时钟。推荐频率24MHz。XXTI and XXTO pins

XUSBXTI:为APLL、MPLL、VPLL、EPLL、USB PHY提供时钟,推荐24MHz。XUSBXTI and XUSBXTO pins.

XHDMIXTI :27MHz,VPLL、HDMI PHY为TV解码器提供54MHz时钟。XHDMIXTI and XHDMIXTO pins

补充:我们的210芯片,一般是从XXTI这个接口进入,这个接口连接外部晶振(规定是24MHz),然后进入内部时钟发生器(syscon),再分别进入4个PLL,分别产生4种不同的高频时钟,各个高频时钟再经过内部的分频器分频得到各种频率的时钟。

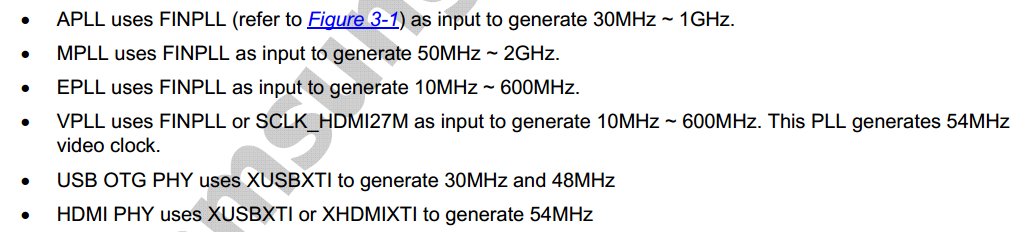

下面是各种PLL可以产生的时钟的频率的范围:

3.s5pv210推荐时钟设置:

HCLK_DSYS:DSYS时钟域的高频率线;

PCLK_DSYS:DSYS时钟域的低频率线;其他的依次类推

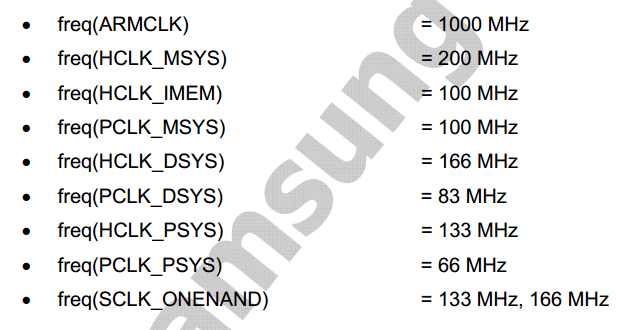

4.分频框图

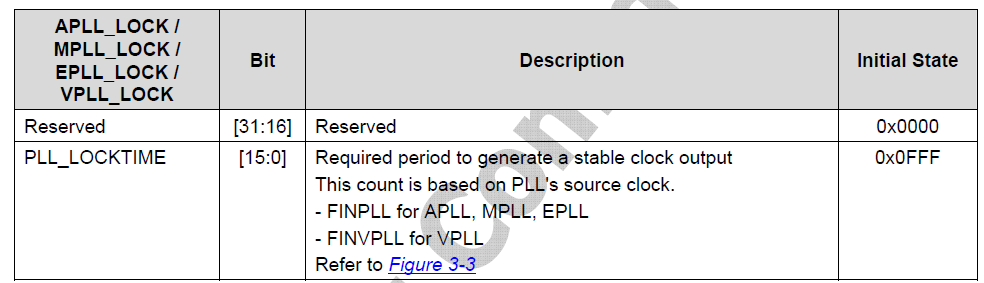

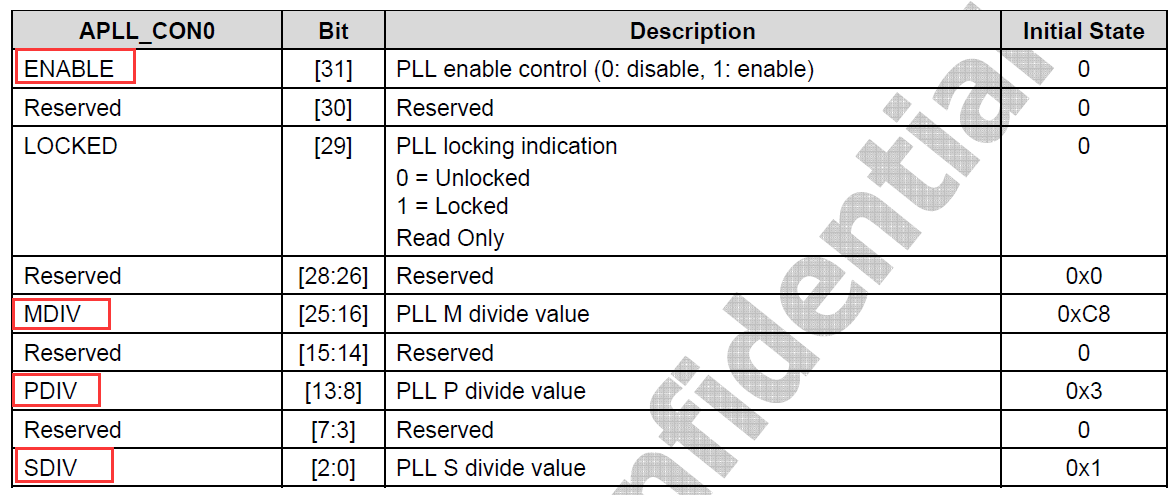

5.相应寄存器

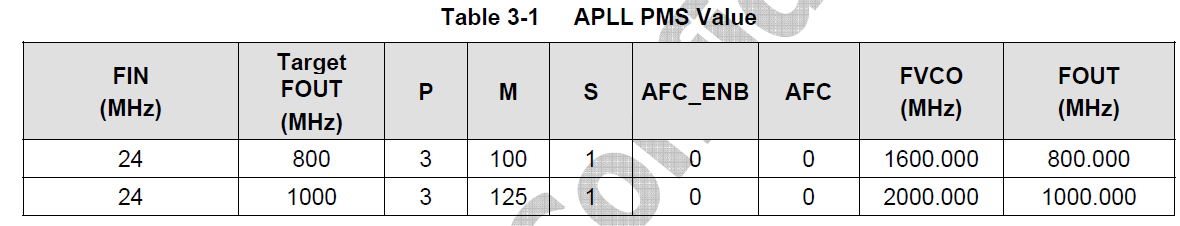

FOUT = MDIV X FIN / (PDIV × 2SDIV-1)

频率1000 MDVI:125、 PDIV:3、 SDIV:1;FOUT = MDIV X FIN / (PDIV × 2SDIV-1) 根据公式计算 FOUT = 1000MHz;

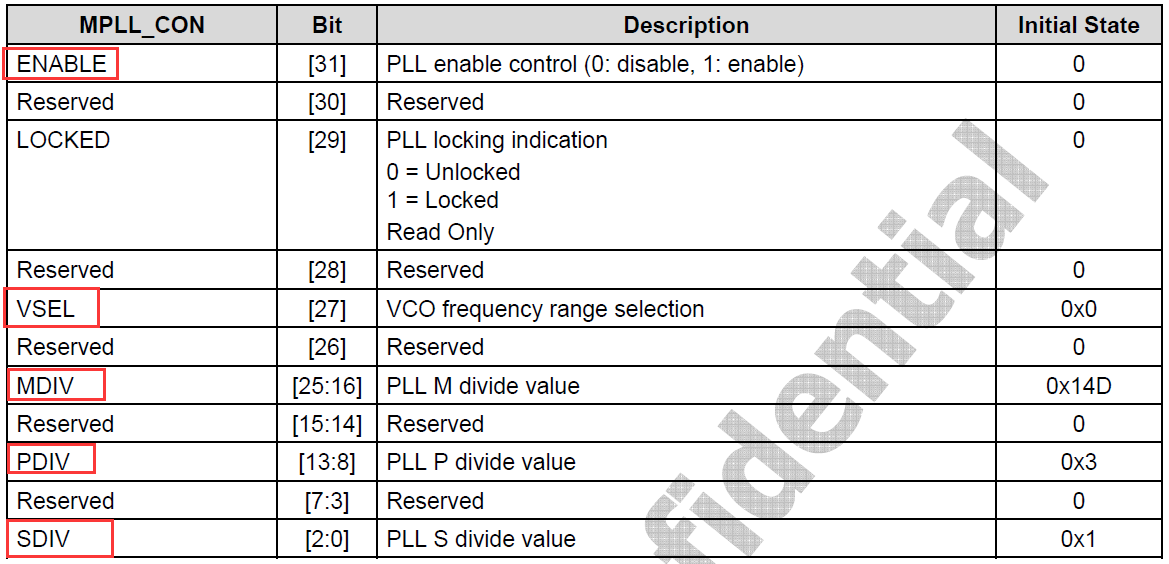

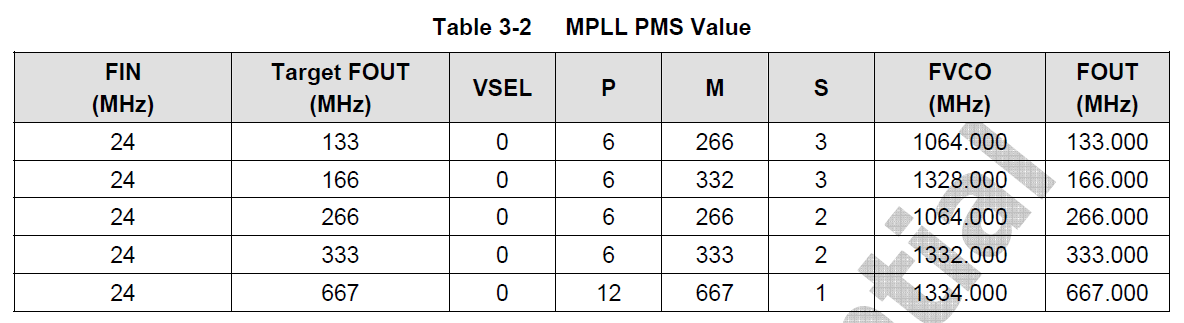

3、MPLL_CON:寄存器,设置MPLL的倍频率

FOUT = MDIV X FIN / (PDIV X 2SDIV)

SDIV:1、 PDIV:12、 MDIV:667;FOUT = 667MHz;

4、CLK_SRC0 寄存器,设置MUX开关

补充:

SCLKA2M, HCLK_MSYS, and PCLK_MSYS are 1GHz, 667 MHz, 400 MHz, 200 MHz, and 100 MHz,

respectively.

代码:

补充复习图:

- 07 初始化时钟

- 时钟初始化

- 时钟初始化

- 时钟初始化

- mc9s08lg32 时钟初始化

- s3c24xx的时钟初始化

- 初始化本地软时钟

- S3C6410 时钟初始化

- S3C6410 时钟初始化

- S3C6410 时钟初始化

- S3C6410 时钟初始化

- s3c6410时钟初始化

- S3C6410 时钟初始化

- ARM-Linux时钟初始化

- S3C6410系统时钟初始化

- 时钟初始化代码

- s3c6410的时钟初始化

- S3C6410时钟初始化

- LeetCode 103. Binary Tree Zigzag Level Order Traversal

- 鼠标移动上鼠标指针各种变化

- (二)UI

- 系统广播大全

- POJ 2676 Sudoku1 (DFS)

- 07 初始化时钟

- 设计中各单位的转换px、pt、ppi、dpi、dp、sp及IOS的分辨率

- POJ 1470 Closest Common Ancestors

- n皇后(位运算版)

- Http Handler 介绍

- SparkRDD缓存策略

- 微服务之分布式跟踪系统(springboot+zipkin+mysql)

- 剑指Offer系列-面试题12:打印1到最大的n位数

- C++函数参数和返回值