low powder design

来源:互联网 发布:人活着的意义知乎 编辑:程序博客网 时间:2024/05/22 01:24

今天看了 http://www.cnblogs.com/IClearner/p/6932721.html 的低功耗设计,总结一下截止到rtl的内容:

功耗分为:动态功耗,静态功耗,浪涌功耗,主要介绍前两个

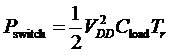

动态功耗:a 开关功耗,主要是因为负载端电容充放电引起的

b 短路功耗,因为输入信号在反转时,信号的反转不是瞬间完成,存在瞬间的短路

静态功耗:主要是漏电流引起的功耗

a 栅极泄露功耗:栅极和衬底之见存在电容,也存在电流,导致的功耗

b 亚阈值功耗:即使没有到阈值,也存在电流导致的功耗

浪涌功耗:开机启动时的最大电流,也称启动功耗。

功耗都可以由工艺库中的功耗模型确定,仿真也都是由这两个决定的。

功耗按照结构划分:时钟树功耗(最多占到30%),处理器功耗,存储器功耗,其他逻辑和ip核功耗,输入输出pad功耗。

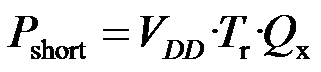

翻转率(Toggle rate,Tr):单位时间内信号(包括时钟、数据等等信号)的翻转次数。如下图所示:

信号在40ns时间内跳转了4次,翻转率为:Tr = 4/4ns = 0.1GHz

另外注意,单位的功耗与状态和路径有关,比如ram的读和写操作的功耗也不同,因为路径不一样,电平一个上升沿,一个下降沿,必然也不一样。

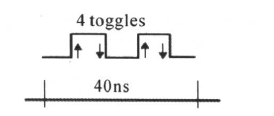

功耗分析流程的输入输出

功耗分析的流程(从输入输出关系看)如下所示:

上面的图中,需要四种东西:

·tech library:这个就是包含功耗信息的工艺库了,比较精确的库里面还应该包含状态路径(SDPD)信息,代工厂提供。

·netlist:设计的门级网表电路,可以通过DC综合得到。

·parasitic:设计中连线等寄生参数,比如寄生电容、寄生电阻,这个一般是后端RC寄生参数工具提供,简单的功耗分析可以不需要这个文件。

·switch activity:包含设计中每个节点的开关行为情况,比如说节点的翻转率或者可以计算出节点翻转率的文件。这个开关行为输入文件是很重要的。这个开关行为可以有不同的形式提供,因此就有后面不同的分析功耗的方法。

(注意,不管使用什么方法进行功耗分析,功耗分析的时候,输入设计文件的都是门级网表文件)

分析信号的翻转,可以使用直接命令输入,设置节点的反转率,也可以使用vcd文件,直接读波形进行分析,最准确。

低功耗分析:

系统和架构级别的低功耗设计:

1.多电压设计技术:每个区域有固定的电压;各电压区域具有固定的多个电压,由软件决定选择哪一个电压;自适应的方式,各电压域具有可变的,由软件决定选择哪一个电压

2.多电压综合时使用到的特殊单元:电平转换器,电源隔离单元,保持寄存器

多电压设计中:供电电压越高,延迟越小,频率越可以高

软件协同设计:

1.软硬件划分 通过合理的软硬件划分,将电压降至最低,同时还能满足需求

2 dvfs 动态电压频率调节 DVFS技术这个种方法属于电压的动态管理,可以通过软件和硬件的方式实现。将DVFS合并到操作系统的调度程序和实时嵌入式任务管理服务当中,利用一个可编程的DC-DC开关电压调节器、一个可编程的时钟产生器和一个宽操作域的高性能处理器等资源进行实现。

3.低功耗软件的动态功耗管理:工作,睡眠,深度睡眠,关闭模式。

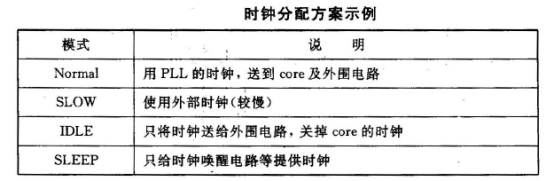

4.系统始终分配:

5.异步设计:同步设计中,增加了很多的缓冲器,导致时钟网络消耗大量的功耗,通过异步,可以减少这部分的消耗。

后面是rtl级别低功耗设计,比较重要。http://www.cnblogs.com/IClearner/p/6908033.html

1.并行方式,如果用两个乘法器取代一个乘法器,时钟频率可以降低整体功耗降低

流水线,流水线就是在组合逻辑之见增加了寄存器,路径长度所短,每个周期只需对M级流水线中的1/M的电容充放电,因而降低了功耗。

2.资源共享

------》

------》

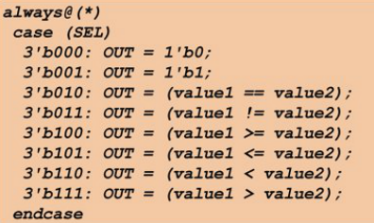

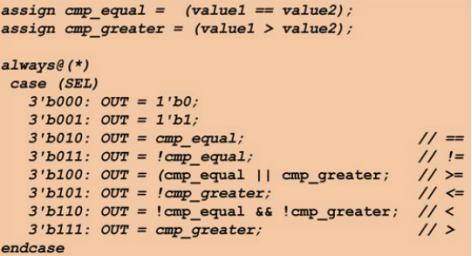

3状态编码,比如使用格雷码比使用二进制反转更少,功耗更低。

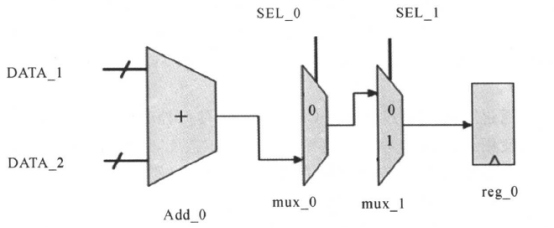

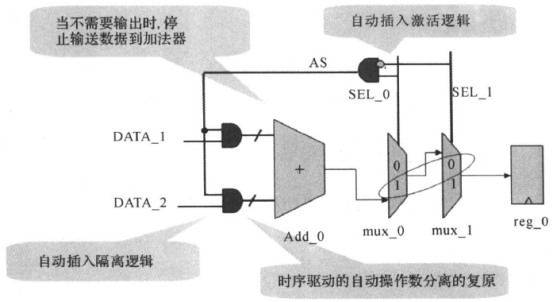

4. 操作数隔离如果在某一段时间内,数据通路的输出是无用的,则将它的输入置成个固定值,这样,数据通路部分没有翻转,功耗就会降低。

----》

----》

注意,此时会增加面积,并影响dft,可以设置为eda自动执行,也可以改为手动执行。

4.门控时钟

http://www.cnblogs.com/IClearner/p/6912455.html

文章里讲了很多,还需自己看。

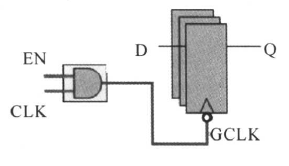

注意的是,简单的门控时钟有毛刺:

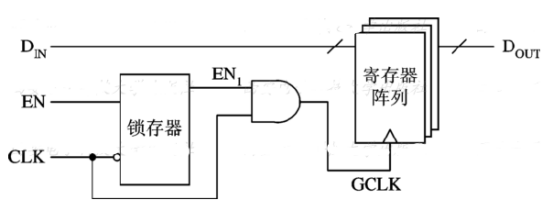

基于锁存器方案的不会存在毛刺现象,因此鼓励使用这一种。

通常情况下,时钟树由大量的缓冲器和反相器组成,时钟信号为设计中翻转率最高的信号,时钟树的功耗可能高达整个设计功耗30%。加入门控时钟电路后,由于减少了时钟树的开关行为,节省了开关功耗。同时,由于减少了时钟引脚的开关行为,寄存器的内部功耗也减少了。采用门控时钟,可以非常有效地降低设计的功耗,一般情况下能够节省20%~60%的功耗。

此外,由于门控时钟不需要用到MUX单元,加入门控时钟电路后,设计的面积也减少了。门控时钟电路的扇出越大,减低功耗和面积的效能越好。当然,扇出太大了,又会产生时序等的问题。

门控时钟电路非常容易实现,用工具自动插入门控时钟,不需要修改RTL代码,门控时钟与工艺无关。

门控时钟可以以三种方式实现:一个与门(即不带锁存的门控时钟)、分散的锁存器+与门、集成的锁存器+与门。在综合库中,与门、锁存器是基本逻辑单元,因此可以构成门控时钟。此外,综合库中还专门提供了集成的门控单元。一般情况下,我们使用的是集成的门控单元,因为这个门控单元是对Skew作了控制,不存在前面描述的毛刺问题。

- low powder design

- Low Power Design Framework

- Direct Rendering Infrastructure, Low-Level Design Document (翻译)

- Magic Powder

- Magic Powder

- Magic Powder

- Magic Powder

- Magic Powder

- Magic Powder

- Magic Powder

- Low Level Design for Identification of the Guest OS Process from VMM:KVM

- powder-puff 花拳绣腿

- powder Designer15问题总结

- powder designer 与数据库

- CF670D2 Magic Powder

- codeforce之Magic Powder

- D2. Magic Powder - 2

- Magic Powder - 2

- HDU 6103 二分求最大子串

- 【SpringCloud】(十一):超时机制和断路器及 Hystrix简单实践

- 2017/7/17~2017/8/7的总结

- qt开发环境

- netty(五) NIO创建的TimerServer源码分析之客户端

- low powder design

- 2017.8.10

- memset

- 调整数组顺序使得奇数位于偶数前面

- strcpy与strncpy

- 【干货】程序员总结java学习工作需要的1000+英语单词带解释!

- 我的微信小程序项目进入测试啦

- PCM A律μ律编码

- 初识JS定时器