芯片——摩尔定律的传奇(下)

来源:互联网 发布:淘宝客服怎么认证 编辑:程序博客网 时间:2024/05/08 21:23

芯片——摩尔定律的传奇(下)

引自: http://www.ccf.org.cn/c/2017-08-16/603629.shtml

50多年来,集成电路(IC)一直按照摩尔定律前行。但是,IC芯片的密度和计算机的速度能够一直按照摩尔定律前行吗?又有哪些物理极限和技术极限需要突破?最小晶体管到底可以由多少个原子构成?是否有能够替代硅的电子集成制造技术?这些问题困惑并激励着人们去寻找新的突破口。摩尔定律会把我们引向何方?

底层有足够空间

1959年,著名科学家理查德·费曼(Richard P. Feymann, 1918~1988)在美国物理学会上作了一次《底层有足够空间》的报告。学术界普遍认为,以该文为标志,人们开始了微纳技术的研究。IC技术的发展也证明了费曼的这一观点。

IC芯片越做越小,而功能越来越强,这得益于光刻技术和微纳技术的发展。1971年,英特尔(Intel)开发出第一代也是世界上第一个微处理器芯片4004,包含了4个芯片,由2300个晶体管组成。该微处理器是为便携式计算器而研发的,供应给日本计算器制造商。英特尔的第二款微处理器芯片8008被用到计算机中,推动了微处理器芯片的研发。1982年,英特尔的微处理器80286采用了1.5μm的工艺,计算机的主频为10MHz,芯片面积68.7mm2;2000年,奔腾4由4200万个晶体管组成,芯片面积224mm2,采用0.18μm工艺;2008年,i7微处理器的晶体管已达7.31亿个。

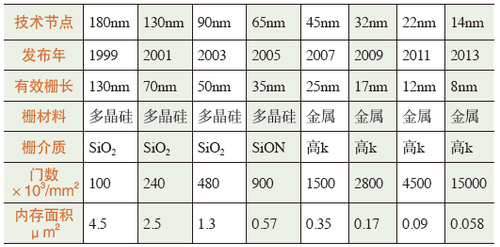

表1 1999年后CMOS工艺技术节点及其部分参数

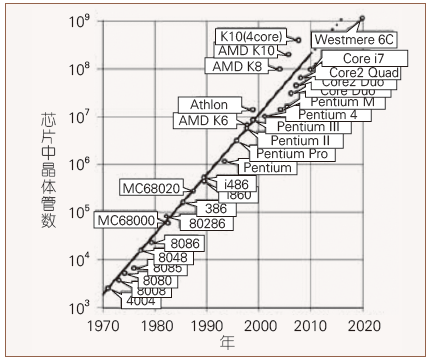

一般来说,现在把互连金属线条间距离的一半称之为半间距,可用来衡量或定义每一代技术的节点。光刻中临界尺寸或最小特征尺寸取决于光源波长和数值孔径等因素,临界尺寸是所定义的半间距的两倍。按照尺寸缩比要求,每两年或三年工艺中最小线条技术节点的尺度要缩小到原尺寸的70%。用标度因子表示为S=0.7×,称之为登纳德标度。理想的同比例缩小是指每一代产品,其场效应管沟道长、宽、栅极氧化层的厚度、结深、电源电压、阈值电压等都要缩小,并按照这个因子来计算。1995年,英特尔推出高性能奔腾处理器,技术节点和实际栅长均为350nm。从350nm以下,每一代产品中该数值只是名义上的标称数值了。实际上,CMOS结构中多晶硅的门长度要比这个技术节点数值更小。2011年,英特尔基于22nm工艺制作了一种四核常春藤桥处理器——“Ivy Bridger, Core i7”芯片,在160mm2上有14亿个晶体管。2015年以后,有了更小的加工线条,如10nm、7nm、5nm等。比如,现在采用紫外光(UV)光刻、电子束曝光,甚至X射线光刻方式,可以制备小于10nm以下的加工线条。表1是1999年以后CMOS工艺技术节点及部分参数。图1是一个典型产品的晶体管数与年代的关系。技术节点的含义随时间也在不断发生变化。近些年,受控于各大半导体公司,技术节点名称只是名称而已,与具体的数值无太大相关性了,但总的来说,与最小特征尺寸有关。对DRAM来说,光刻的线条半宽越小越好;对MPU来说,栅长越小越好。

图1 典型产品的晶体管数与年代的关系

(图片来源:Design and Modeling for 3D ICs and Interposers: pp.1-59. 2013)

闪存是日本东芝公司舛冈富士雄(Fujio Masuoka)于1984年发明的,是一种可移动的电可擦写存储介质,结构类似MOS管器件,在沟道和栅极之间有一个氧化绝缘包裹的多晶硅浮栅,用于存储电荷作为信息。闪存的结构特征尺寸已经达到14nm。2005年,闪存的容量是2GB;2008年,16GB;2009年,32GB;2011年,64GB。2013年,128GB,包含640亿个元件,已经是当初摩尔预言的65000个元件数的100万倍了。这个数字相当惊人。同微处理器相比,闪存不属于电发热器件,它只有在写入或擦除信息的时候才消耗很少的电。因此,可以多层叠加在一起,其密度相当大。

难以想象的微纳晶体管制造技术

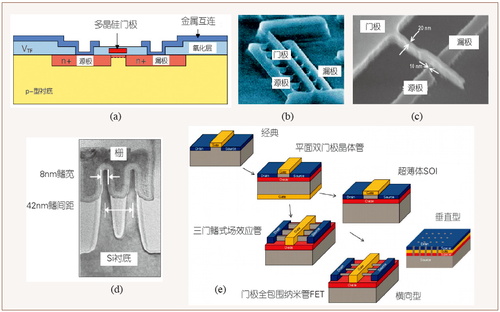

为了提高芯片运行速度和密度,能对更多的结构单元进行控制,就要不断缩小晶体管的尺寸和晶体管间的距离,这正是摩尔定律一直追求的。晶体管的MOS结构由源极、栅极和漏极组成,其工作原理是,通过改变栅极电压来控制电子在源极和漏极之间的运行,从而具有电子开关的作用。缩小晶体管的关键是把负责控制的栅极长度缩小,栅极的长度就是电子要跨越的距离。当栅极的长度与源极和漏极耗散结宽度之和相近时,会出现短沟道效应。栅极尺寸缩小带来两个主要问题:一个是晶体管栅极缩小时,漏电流不断增加;另一个是源极、漏极、衬底间、电极接触处寄生电阻和电容的影响相对变得越来越大。图2(a)是一种常规的场效应晶体管(FET)。相对来说,栅极沟道越短,电子渡越时间越快,耗电也越少。

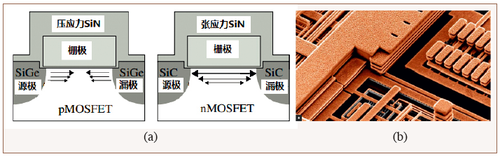

应变硅技术是一种在保持晶体管栅长度不变时提高速度的主要方式,是2003年进入100nm节点以下之后采用的一种技术手段。该技术通过改变面心立方单元中硅原子的位置,提高载流子的迁移率,从而提高晶体管的电流和增益。该技术是由英特尔于90年代发明的。比如,在SiGe层上生长一层硅,导致硅层的晶格膨胀,硅原子间处于拉伸状态,产生应变,硅原子间相互作用力减弱,使硅中电子速度提高,从而使控制晶体管的开关速度提高。反之,若硅原子处于压缩状态,则电子速度变慢。一种途径是在晶体管的源极和漏极采用掺杂锗,在p沟道MOSFET中产生压应力,提高空穴的迁移率;或掺杂碳来控制n沟道MOSFET中产生张应变,进而改变电子的迁移率。还可以在多晶硅栅极周围生长氮化硅产生水平张应力或压应力,使沟道中硅原子处于拉伸或压缩状态,电子或空穴的运动速度加快。图3(a)是结合源漏区掺杂SiGe(SiC)与栅极包裹层压(张)应力增强p(n)沟道空穴(电子)的应变MOSFET。应变硅为沟道的技术是在90nm以下技术中主要采用的方式,而2011年前则采用常规的硅来做沟道。

图2 (a)平面n沟道MOSFET晶体管示意图 (b)多门多鳍晶体管 (c)一个10nm的晶体管 (d)14nm工艺中一个三门晶体管的鳍微观结构图 (e)目前晶体管结构发展示意图

(图片分别来源:(a)Microelectronics in the “More than Moore” age: becoming a truly pervasive technology, Ford Motor Company conference Center and the Henry Ford Museum, May, 2013;(b)Moore’s law: the future of Si electronics, materials today, June 2006, V9N6;(c)Sub-20nm CMOS FinFET technologies, IEEE IEDM, pp.421-424,2001;(d)14nm process technology: Opening new horizons, Intel;(e) Are Nanotube Architectures More Advantageous Than Nanowire Architectures For Field Effect Transistors, Sci.Rep 2.doi:10.1038/srep00475, 2012)

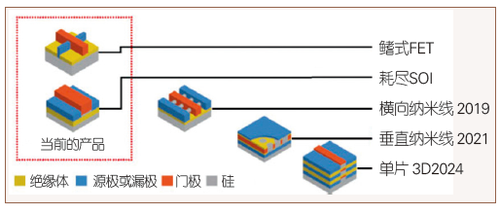

为了解决漏电流问题,有两种主流设计制造方式能有效地抑制短沟道效应:一种是在绝缘衬底上设计的超薄体UTB-SOI场效应管(MOSFET)(ultra thin body SOI, UTB);另一种是双门或多门鱼鳍式场效应管(FinFET),如图2(b)、(c)和(d)。在鱼鳍式非平面场效应管中,通过对源极与漏极间导电沟道“硅鳍”进行两面或三面氧化绝缘包裹,从而有效地抑制漏电流。图2(c)是一个鳍式场效应管,源极与漏极像鱼的左右鳍,栅极则相当于鱼脊。可采用多晶硅包裹源极与漏极的硅鳍作电连接,多晶硅能有效地降低接触电阻并能和金属有效地互连。图2(d)是英特尔在14nm工艺中制备的一个三门控制FET鳍的微观结构图。图2(e)是晶体管从最初经典的构架发展到鳍式晶体管等的构架示意图。从中可以看到晶体管结构的发展模式:从利用普通硅到利用绝缘衬底SOI(Silicon-On-Insulator)硅片,从单门控制发展到双门和多门控制,从平面结构发展到非平面结构,从水平方向晶体管构架发展到垂直晶体管构架。总而言之,是通过各种绝缘电控的方法在最大程度上控制晶体管中源极到漏极的电子输送,以减少漏电流。未来IC发展中,该FinFET结构将是一种主要的构架方式。

抑制漏电流可以显著提高晶体管的可靠性。数据表明,当氧化层的厚度减小到1nm时,由于量子遂穿效应,电子将要穿越氧化层,产生显著的漏电流,对电子的控制越来越难,这时就需要采用高介电常数(k)的材料来替代二氧化硅做绝缘层,比如氮氧硅铪(HfSiON)和二氧化铪(HfO2)。数据表明,英特尔于2007年在45nm工艺节点中开始采用带隙宽的高k材料,这提高了栅极电容,从而极大降低了漏电流;同时,晶体管的栅极也由多晶硅电极转变成金属电极,以抑制多晶硅在加电压时产生耗尽区,使驱动电流性能降低。45nm技术包含了高K、金属门、应变硅、9层铜互连、193nm光刻,以及无铅封装等。

以铜/低k(低介电常数)作为互连极大地提高了IC的性能。IC中电信号的速度由两部分控制:一个是单独晶体管的开关时间,即栅极门延迟时间;另一个是晶体管之间的传输时间,即RC延迟(R是电阻,C是电容)。在微米尺度以下,RC延迟变得非常明显。解决的途径是降低互连电阻和电容。1997年,IBM公司宣布,利用铜布线可以使微处理器更快、更小,而且成本更低。由于铜比铝的电阻率低40%,其运行速度可提高15%。2001年,电互连开始采用铜替代铝膜。为了减小电容效应,将隔离铜的氧化物采用低k(同二氧化硅相比)材料来代替,如采用掺氟的氧化物和氟硅玻璃(FSG)等来降低电容。因此,在130nm工艺中,铜/氟硅玻璃作为互连是一种解决方案。图3(b)是IBM制备的多层铜工艺图片,结构层层叠叠,宛若迷宫。

图3 (a)源漏区掺杂SiGe(SiC)与栅极包裹层压(张)应力增强p(n)沟道空穴(电子)的

应变MOSFET(图片来源:Strain Engineering for CMOS Devices, IEEE,2006);(b)IBM制作的多层铜布线(图片来源:http://www-03.ibm.com/ibm/history/ibm100/us/en/icons/copperchip/)

从1975年到2012年,芯片的单元密度和工作速度的增长率一直在稳步提升。2010年的国际半导体技术路线图预言,芯片密度的增长率在2013年将放缓。2015年,摩尔本人更是预言,摩尔定律在下一个十年将走到尽头。英特尔公司首席执行官布莱恩·科兹安尼克(Brian Krzanich)也说,从2012年的22nm技术开始,芯片的发展速度已经慢下来了,这将一直持续到14nm的技术节点,我们现在更新换代的周期大约接近两年半的时间。2016年4月,他又说,在他34年的半导体工业生涯中,他见证了四次宣称“摩尔定律的终结”。但他们从14nm向10nm进军,并计划7nm和5nm,甚至更小尺寸时,他们的计划一直是按照摩尔定律前行的。

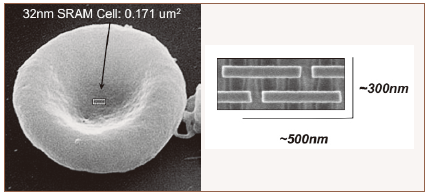

可以预言的是,随着新技术的出现,摩尔定律将会继续向前。最新的微处理器其特征的鳍结构只有14nm,这比大部分病毒(100nm)还小,如图4所示。实际上,当栅长小于10nm时,器件对其实际尺寸和材料组份的变化会非常敏感。有人估计,当基于硅的芯片特征尺寸达到5个原子时,电子的漏电流和海森堡测不准原理的效应将显现,器件将不再实用。而至今还没有什么材料可以取代硅。

图4 英特尔在32nm工艺中制造的一个SRAM放置在一个人体的红细胞上,右侧为SRAM微观结构。(图片来源:Variation in 45nm and Implications for 32nm and Beyond,2009 2nd International CMOS Variability Conference –London)

超越摩尔

超越摩尔(More than Moore, MtM)的概念是在2005年的国际半导体路线图中提出来的,目的是描述按照摩尔定律,芯片不再适合小型化发展趋势下的技术特征。这些技术突出了非数字化功能,比如无线通讯、功率管理、敏感检测和执行,即将这些新功能集成到片上系统(System-on-Chip, SoC)或系统级封装 (System-in-Package, SiP)中。片上系统是将多种功能集成到一个芯片中,而系统级封装却是将多个芯片集成到一个封装模块中(不是在PCB板上)。而2015年的半导体路线图中又将异质集成(Heterogeneous integration)提出来,即将不同制造方法制作出来的元件集成到一起,旨在增强功能。因此,需要一套新的物理参数和优化指标来表征正在显现的技术。

如果只按照晶体管不断缩小的方式走下去,必将受制于物理定律,我们终究要走进一个死胡同。人类的智慧在于不断发现新的方法和途径。据报道,NEC公司于2002年制作了门长只有6nm的晶体管。图5是未来晶体管的发展趋势。比如从目前的鳍式FET,将要发展到以纳米线、纳米管为电子输运通道的晶体管,在二维和三维方向也不断扩展,晶体管的制造将发生本质的变化。

图5 未来晶体管发展趋势

(图片来源:http://spectrum.ieee.org/semiconductors/devices/transistors could stop shrinking in 2021)

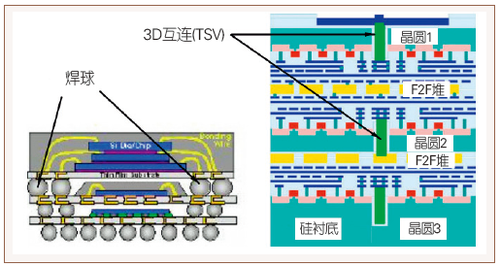

为了提高IC的密度和功能,IC技术的发展从平面技术扩展到三维技术,从单芯片扩展到多芯片模块(MCM)方式。为了降低功耗和散热,提高计算机的运行速度,芯片从单核发展到多核,也从单一功能发展到多功能等。但问题随之出现了,比如由多芯片模块构成的系统,片间互连距离陡增,极大地破坏了系统的性能。90年代中期片上系统的到来就是为了解决离片互连所带来的延迟问题。将所有组件全部集成到单一衬底上将极大提高系统的速度,同时降低功耗。系统级封装是另一种通过将多个芯片堆垛的方式并通过引线键合的解决方案。此外,基于硅通孔(TSV)的三维集成技术也是目前人们关注的一个集成方案。多层结构、金属互连、转接板和硅通孔等方法和技术成为研究的一个切入点,这对系统集成提出了更高的要求。比如,在65nm技术中,晶体管的门长减小到35nm,氧化层厚度为1.8nm,有8层金属铜互连。图6展示的是一种系统级封装与三维集成技术的互连方式。

图6 系统级封装与三维集成技术的互连方式

(图片来源:Springer International Publishing Switzerland 2015, Three-Dimensional Design Methodologies for Tree-based FPGA Architecture)

摩尔之外还有什么呢?还有更加丰富多彩的世界,基于硅的微机电系统(MEMS)展露了它前所未有的生机和活力。还有微机电系统、传感器、光电二极管、功率器件、三维封装和异质集成方案等。

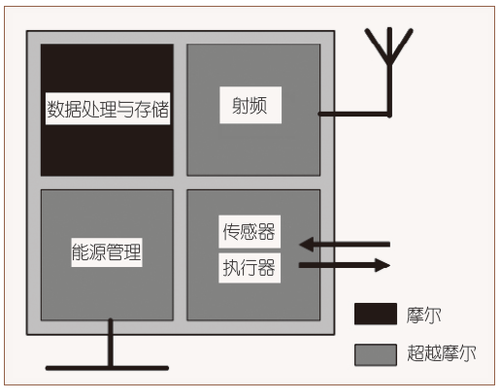

在制造工艺上,光刻方法加工的线条不可能无休止地缩小下去。一种解决途径是寻找和利用新的沟道材料和器件,如碳纳米管和纳米线,以及上述三维的制造方式等。图7是一个典型的包含多个“摩尔”和“超越摩尔”的微系统,数据处理与存储属于摩尔范畴,而新型传感器、射频乃至能源管理都成为超越摩尔之中要考虑的内容。除了热问题之外,能源问题是超越摩尔系统所要解决的一个突出问题。曾经的计算只局限于台式机和超级计算机,而今计算已经步入移动时代,智能手机要利用WiFi和GPS,网络不断地、长时间地和周边以及其他用户通讯工作,要与各种传感器,比如触摸屏、磁传感器、加速度传感器进行交互作用,计算量很大,需要消耗的能量也很大。

图7 一个典型的包含多个“摩尔”和“超越摩尔”的微系统

(图片来源:Positioning More Than Moore Characterization Needs and Methods Within the 2011 ITRS)

摩尔定律的内在驱动力

究竟有哪些因素在推动摩尔定律向前发展呢?无疑,是市场极大的需求和巨大利润的吸引。60年代IC发展的初期,仙童半导体公司生产的晶体管和逻辑电路芯片就得到美国很多重大工程的订单。仙童半导体公司当时占有IC市场30%的份额。

研究表明,自半导体工业诞生以来,有三个商业驱动力在推动半导体向前发展:一是计算机工业的到来推动了内存的需求;二是专用IC的发展;三是IC允许多功能系统的集成。

研究还表明,软件代码行数也呈指数增长规律。1995年,微软首席技术执行官研究了软件代码行数。他发现,1975年,Basic语言的编译器只有4000行;而20年后,几乎达到了50万行。软件的规模和复杂度在增加,也需要越来越快的微处理器。

实际上,半导体工厂的投入也是按照指数增长的。伴随着每一代新品的到来,芯片的研发、制造和测试费用都在稳步提升,这导致摩尔的第二定律,即在半导体作坊上的资金投入也随时间呈现指数增长。摩尔在1995年发表文章说:“最使我担忧的是投入的花费……这是另一个指数。”1966年,一个新的半导体基础设施投入费用约为1400万美元;30年后则达到15亿美元。投入如此巨大,对半导体的发展来说无疑是致命的,一个解决途径是国际间大公司的竞争与合作。而一旦无利可图之时,摩尔定律就很难走下去了。有人说:“摩尔定律的终结不是技术问题,而是经济问题。”

摩尔定律促使人们在许多方面进行创新和突破,提出新思想、新技术来解决一些技术瓶颈。基于新的物理原理的原型样机,如量子计算机和神经网络计算机等将成为人们期待的运算工作模式。为了拓展和深入摩尔定律,2016年,美国半导体工业年会报告的路线图题目为“国际器件与系统路线图”。大会主题不再聚焦跟踪摩尔定律,而是转向应用,如智能手机和云数据中心等,研究应该开发什么样的芯片以支持这些功能和应用。

2015年,摩尔再次预言,IC前进的速度将趋饱和,估计下一个十年左右,摩尔定律或将终结。不过半导体展望家卡弗·米德(Carver Mead)在1992年写到:“摩尔定律是一件有关人类活动的,是关于眼界的……许多人被他们的知识和信仰所限制,从而不能越雷池一步。当摩尔做出他的预言时,他让我们认识到是什么在前行……我们一直处于一个动态的、不断前行的世界中。”爱因斯坦曾这样说过:“科学家研究的是早已经存在了的,而工程师将创造的是前所未有的。” ■

- 芯片——摩尔定律的传奇(下)

- IT领域的奇葩解读——反摩尔定律

- 失去光泽的太阳—反摩尔定律

- 摩尔定律终结——后摩尔时代,何去何从?

- 开源界的摩尔定律

- 摩尔定律的危机

- 摩尔定律的终结

- #摩尔定律的生死存亡

- 摩尔定律的失效

- 摩尔定律的现实意义

- 摩尔定律的现状

- 手机行业背后的摩尔定律和反摩尔定律

- 对摩尔定律的理解

- 对摩尔定律的理解

- “逐渐失效”的摩尔定律

- 对摩尔定律的思考

- IT领域——摩尔定律会不会失效

- 摩尔定律

- java注解详解

- OpenResty--LUA用FFI库调用C函数实例

- 1031. Hello World for U (20)

- springmvc与spring父子容器controller扫描机制

- “码工”下足笨功夫 二维码门牌更智慧

- 芯片——摩尔定律的传奇(下)

- webservice接口编写

- Django中REST风格数据传输

- web安全之CSRF

- fatal: refusing to merge unrelated histories

- C#高级应用之CodeDomProvider类

- 文档格式转换技巧全记录,超完整的文档格式转换方式

- Fragment+webview实现物理返回键的监听

- 手机号、银行卡号格式化