【转载】Nios II 嵌入式系统硬件设计(三)之Flash控制器参数设置及硬件电路连接

来源:互联网 发布:ff14猫男捏脸数据 编辑:程序博客网 时间:2024/04/29 21:39

呵呵,flash的时间设置一直没弄明白,看了这篇文章总算有所收获,

转自:

http://bbs.ednchina.com/BLOG_ARTICLE_182247.HTM

Flash是非易失性存储器,可以在断电后保存程序或数据内容,相当于电脑的硬盘,而SDRAM则相当于电脑的内存,所以,nios开发板的flash和SDRAM器件基本是标配。

前几篇文章已经讲述了SDRAM控制器的参数设置及其硬件电路连接,下面讲讲flash设备控制器的参数设置及其硬件电路连接。

一、 flash控制器参数设置

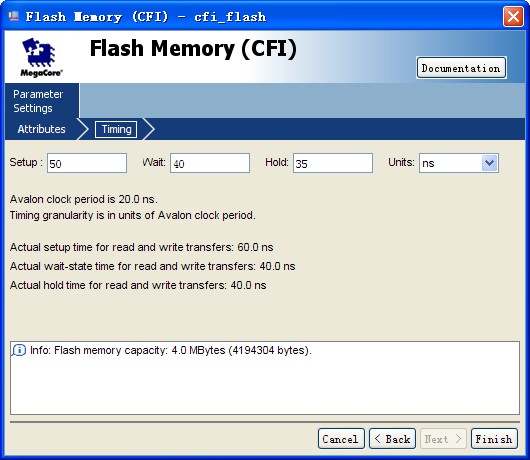

在SOPC中加入flash memory(CFI),弹出如下对话框,

Attributes标签

在presets中预设了一些常用的flash设备,选择一种flash后,会将标签中的值设置为与该flash相匹配的相应值。Nios系统支持的flash基本是AMD和intel的,其他厂家的flash可能不一定支持。如果没有预设的器件,则选择custom,用于根据flash的datasheet自定义。

在size中填写flash的地址线和数据线宽度。我用的flash是AM29LV320,4M*8bit,所以选择地址线22,数据线8。

Timing标签

在Timing中主要有Setup,Wait,Hold几个参数。

Setup

片选有效后,发起读或写信号之前所需的时间。可以有如下公式计算:

Setup = tCE (chip enable to output delay) - tOE (output enable to output delay)

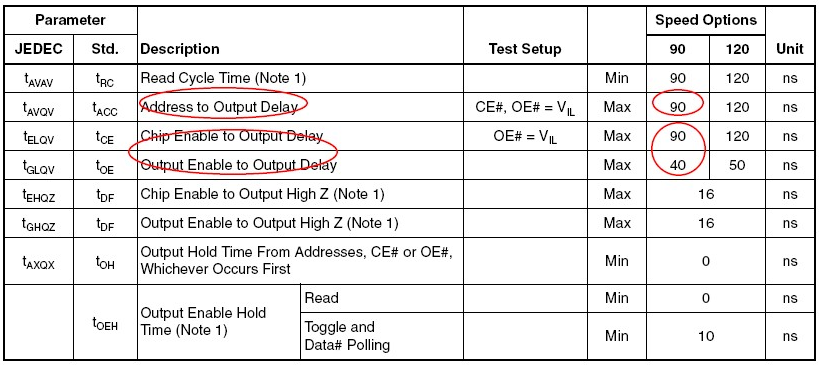

tCE,tOE可以在flash的datasheet中查询得到,

根据上面表格得出tCE=90ns,tOE=40ns,所以Setup=50ns。

Wait

对于每次传送,使能读/写信号所需的时间。该参数需要满足如下规则:

Setup,Wait和电路板级延时的和一般要小于tACC (address to output delay),电路板级延时主要是FPGA中flash地址线的TCO,falsh数据线的TSU,以及走线的延时。电路板级延时很小,在这里我们将其忽略,这样,Wait=tACC-Setup=40ns

Hold

写信号无效后,使片选无效之前所需要的是时间。这个参数没有在datasheet上找到,参考预设flash的值,设置为35ns。

Units

时间单位,这里设置为ns。

如果实在不能确定这些时间的值,还有一个办法是将这些值都设置的较大,比如大于100ns,这样电路应该能正常工作,只不过工作效率会下降,因为花费在每次读取上的时间会增大。

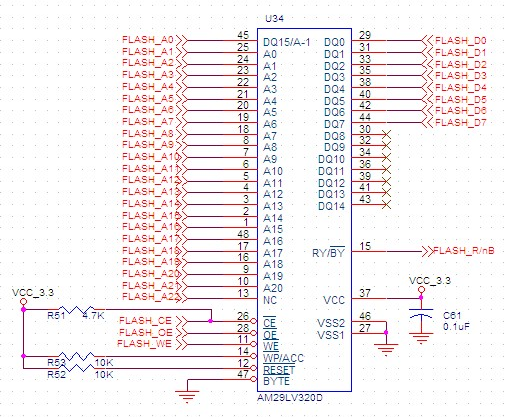

二、 flash硬件电路设计

下面是我自制FPGA开发板上flash部分电路(省略电源滤波部分电路),已经调试通过,电路没有问题,可以放心参考,呵呵。

介绍下主要管教功能:

A:地址线

DQ:数据线

DQ15/A-1:如果是字(16位)读写模式,该位作为数据最高位,如果是字节(8位)读写模式,该位作为地址最低位,在我的电路中采用字节读写模式,所以作为地址最低位。

CE:片选信号

OE:输出使能信号

WP/ACC:该管脚不能悬空,WP:提供硬件写保护功能,ACC:高电平输入时加速flash程序烧写。

RESET:复位信号

BYTE:选择8位还是16位读写模式,低电平是8位。

RY/BY:Ready/Busy输出

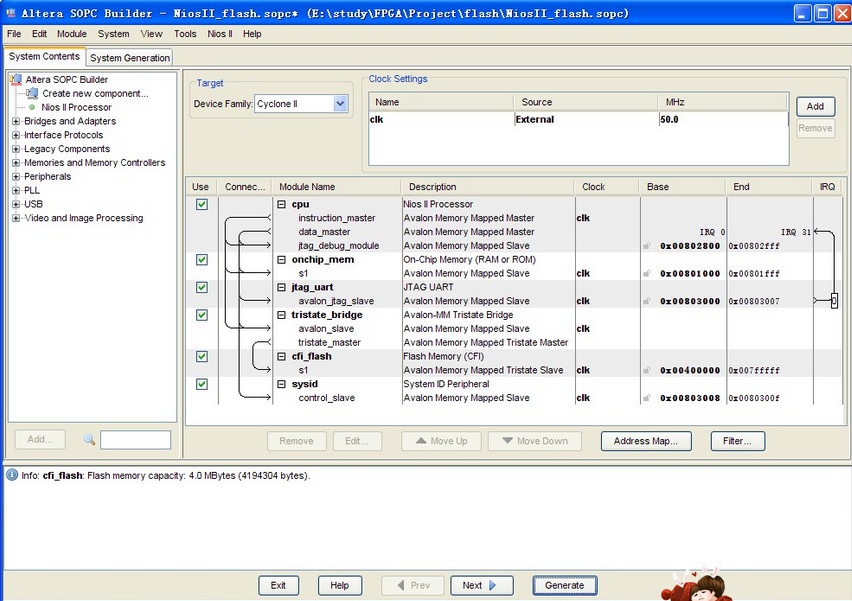

三、 flash控制器电路连接

下面是一个基于flash的nios II 最小系统,因为.rwdata, Heap memory ,Stack memory不能在flash中,所以加了一个4K的onchip_mem。

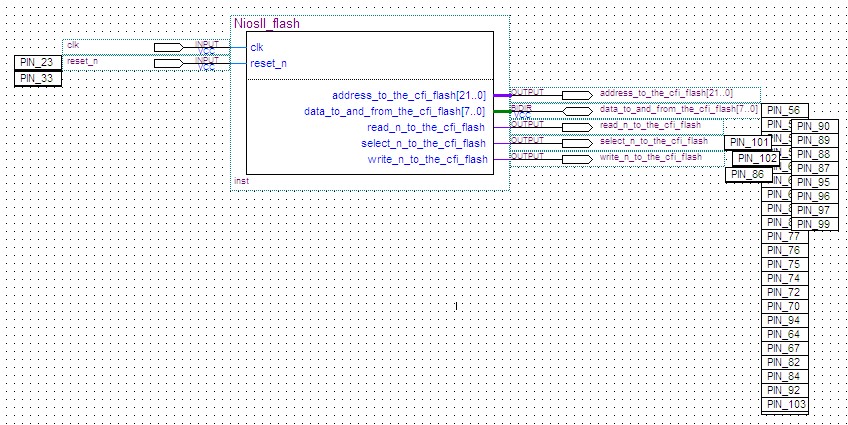

下面是在QuartusII中的顶层电路图连接

- 【转载】Nios II 嵌入式系统硬件设计(三)之Flash控制器参数设置及硬件电路连接

- Nios II 嵌入式系统硬件设计(一)之SDRAM Controller参数设置

- Nios II 嵌入式系统硬件设计(二)之SDRAM硬件设计

- Nios Ii葵花宝典-Nios II嵌入式系统设计教程 之Fedora 13的安装

- 手把手硬件电路详细设计过程(转载)

- BMT硬件之系统(一):单片机、DSP、嵌入式、微控制器的区分

- 读书笔记之《嵌入式硬件设计》

- 硬件电路之电源设计MP2359

- 硬件电路可靠性设计

- 硬件工程师面试集锦 模拟电路 数字电路 IC设计基础 单片机 信号与系统 DSP 嵌入式

- 硬件工程师面试集锦 模拟电路 数字电路 IC设计基础 单片机 信号与系统 DSP 嵌入式

- 如何将Nios II硬件和软件合成一个文件(NIOS II)(硬件)(软件)(合并)

- 嵌入式系统基础知识------之嵌入式的硬件基础(1.3)

- 硬件电路之蜂鸣器

- 硬件电路之开关

- 嵌入式系统硬件电路的各种接地方法总结

- 硬件电路的设计流程(两层板)

- 嵌入式系统硬件原理设计与审核

- SQL日期格式化应用大全

- Allocate aligned memory

- Linux下LCD编程

- [转]建立信任,能力是关键

- 一步一步学Streams第一部分(3)基础之捕获进程

- 【转载】Nios II 嵌入式系统硬件设计(三)之Flash控制器参数设置及硬件电路连接

- Apache Tomcat(一)Apache Tomcat的简单介绍

- 函数指针 指针函数

- socket的创建

- 黑马程序员--学习多线程和Socket小结

- Android 开发图片压缩/缩略图的方法

- android----官方Calendar例子

- Java小结--类、接口

- 一步一步学Streams第一部分(4)基础之传播进程(上)