1.3节 逻辑门与二进制数 part1

来源:互联网 发布:天刀男脸型数据 编辑:程序博客网 时间:2024/05/14 09:11

好了,看过上面一节的内容,让我们继续来搭积木吧~这回我们有了MOS作为积木,我们想搭个什么东西呢?答案是,什么都行只要有创意。主要是学习”搭积木“的思想,看过本系列一定会知道那是什么东东。那么作为启发性的例子,请看下几幅图:

(1)”NOT“门(2)”NAND“门(3)”NOR“门

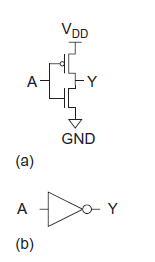

(1)首先看”NOT“门吧,A代表输入(当然只能是1或0),Y代表输出(当然也只能是1或0)。记得上一节说的pMOS那个小泡泡了吗,就是”非“啊。这里也一样通用。当然可以用以下记号表示(定义)Y=~A,其中~符号在本系列里表示“非”运算。

看图(a)当A=1(高电平相对于地)pMOS断开,nMOS导通(可视为导线),就像当于Y直接接地啊!当然输出是0.所以输入1的时候给我返回一个0.。。这不就是对着干么。。就叫它”非“门。同理,当A=0.。。。。。。(省略号自己填,不懂得留言~)。

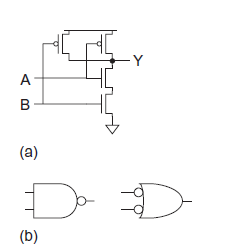

(2)这是神马?!别急,(b)图看到小泡泡--就是非了,但是接了一个拱形的符号,那个被定义为“与”(AND)。“与”意思就是,我和你缺一不可。 举个例子说:定义结婚是个“好”结果(代表输出是1),而结婚的前提是必须有两个人存在,即两个输入必须都是1,只有一个人是没有办法结婚的!AND的表达式是Y=A*B,根据(1),这个符号整体可以写成Y=~(A+B),注意一定不要忘记括号!如果不加括号的话,就是说先“NOT”A的输入再ANDB的输入,结果完全不一样的。这个逻辑门叫做“NAND”(理所当然---NOTAND!“与非”门)再看(a)图,注意图中只有画圆点的地方才代表导线连通。当A=1,B=1的时候,上面两个pMOS都断开,只有下面两个nMOS一起导通,所以当然输出Y为0.那么剩下的所有情况请大家一一推导出来~~~下一节有答案揭晓。

举个例子说:定义结婚是个“好”结果(代表输出是1),而结婚的前提是必须有两个人存在,即两个输入必须都是1,只有一个人是没有办法结婚的!AND的表达式是Y=A*B,根据(1),这个符号整体可以写成Y=~(A+B),注意一定不要忘记括号!如果不加括号的话,就是说先“NOT”A的输入再ANDB的输入,结果完全不一样的。这个逻辑门叫做“NAND”(理所当然---NOTAND!“与非”门)再看(a)图,注意图中只有画圆点的地方才代表导线连通。当A=1,B=1的时候,上面两个pMOS都断开,只有下面两个nMOS一起导通,所以当然输出Y为0.那么剩下的所有情况请大家一一推导出来~~~下一节有答案揭晓。

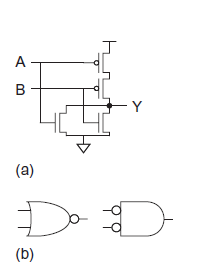

它旁边那个记号的输出(Y)等同于AND的输出,只是实现方式不一样。注意把那两个小泡泡拿掉的话,这个符号叫做“或”(OR)门。先把输入“非”一下然后再“或”(OR)一下。而OR的就好比吃饭的时候为了能吃到嘴里(就是为了结果为1),你可以用筷子也可以可用手抓~~~,记号是Y=A+B。所以整体的记号是Y=(~A+~B)。其实如果有兴趣,你可以叫它“非或”门。。。这两个门为什么等同呢?想一想怎么证明,下节会有答案哦。(提示:(1)可以把所有输入和输出的情况列出来,因为也就是0和1嘛(2)观察电路图(a),从不同的角度看待同一个问题会有不同的见解!)

(3)这一组当然就是“NOT”和“OR”的组合了也就是“NOR”门咯,利用(2)讲的就应该能写出表达式咯。写完后参考一些:左边的图表达式Y=~(A+B),其等同的实现也就是右边的图Y=~A*~B(译成汉语就是“非”A“与”“非”B)。

举了上面这三个例子,大家看出来一些头绪了没。看所有例子里所有门的电路图,都会有pMOS和nMOS参与工作,所以这个叫做CMOS~就是互补MOS嘛,所以CMOS不是一个晶体管而是两个或两个以上MOS的集合!而一般带有pMOS的在“上面”,nMOS在“下面”--所以分别被叫做“上拉网络(pull-upnetwork)”,“下拉网络”(pull-downnetwork)。所谓“上面”就是定义为让输出Y和高电平(VDD)相连的部分,而“下面”自然就是让输出Y和低电平VSS相连的部分。----------讲到这里,有人可能会发现有问题了:如果上拉是断路,下拉也是断路,输出怎么办?反过来上拉和下拉都是打开,岂不是要短路~~没错!第一个情况就是y会处于不确定状态,比如你用手碰一碰,静电的值会决定y,所以这时y的输出被称为“浮动Z(floatingz)”输出。而第二种情况就是Y无法决定取0和1哪一个值,而由高电平源源不断的向Y输入不稳定电压,从而损失静电能。那么这个状态就被称为“X”(contentionX)。

好了,这一小部分最重要的是用一张纸,和一支笔写一写推一推我提出的小问题。下一小节给出形式化的答案~

本文出自 “从基础走向大师” 博客,请务必保留此出处http://physic.blog.51cto.com/1656469/1305029

- 1.3节 逻辑门与二进制数 part1

- 1.3节 逻辑门与二进制数 part2

- 1.3节 逻辑门与二进制数 part3

- 1.3节 逻辑门与二进制数 part4

- 1.3节 逻辑门与二进制数 part5

- 3.二进制数的应用、逻辑学及逻辑门

- 传感器状态与二进制数

- 二进制数与汉诺塔问题

- 十进制数与二进制数的转换

- 二进制数、八进制数、十六进制数与…

- 二进制数与十六进制数之间如何互相转换

- 二进制数

- 二进制数

- 逻辑中的二进制

- 继电器与逻辑门

- 32位二进制数与16位二进制数相乘,在屏幕上输出结果

- 字符串与二进制数之间的互相转换

- 字符串与二进制数之间的互相转换

- [深入浅出Cocoa]iOS网络编程之CFNetwork

- 从VLSI设计到计算机架构系列-序

- 第一章1.1 回顾CMOS的一些知识

- 1.2节 MOS基本构成

- 1.2节 MOS基本构成 --续

- 1.3节 逻辑门与二进制数 part1

- 1.3节 逻辑门与二进制数 part2

- 1.3节 逻辑门与二进制数 part3

- 开关电源设计入门到精通系列--序

- 1.3节 逻辑门与二进制数 part4

- 1.3节 逻辑门与二进制数 part5

- 1.4三态缓存(tristate buffer)与 多路复用器(Multiplexers)

- 第三章 3.1 精通HDL语言:Verilog,VHDL -序

- 1.5节 卡诺图以及布尔代数(SOP,POS)part1