1.3节 逻辑门与二进制数 part4

来源:互联网 发布:java 枚举声明 编辑:程序博客网 时间:2024/05/29 04:30

晚上好忙,顺便透露一下,忙着搞引力理论~~这个是我的专业,有兴趣的朋友一起来讨论哦。回到我们的Transimission Gate (传送门)来。根据上一部分讲的MOS的特性(例,pMOS善于传递“1”而不善于传递“0”),那么我们要设计一个电路,既能很好的(strong)传递1也能和好的传递0怎么办呢?很简单,把nMOS和pMOS并联在一起不就好了。

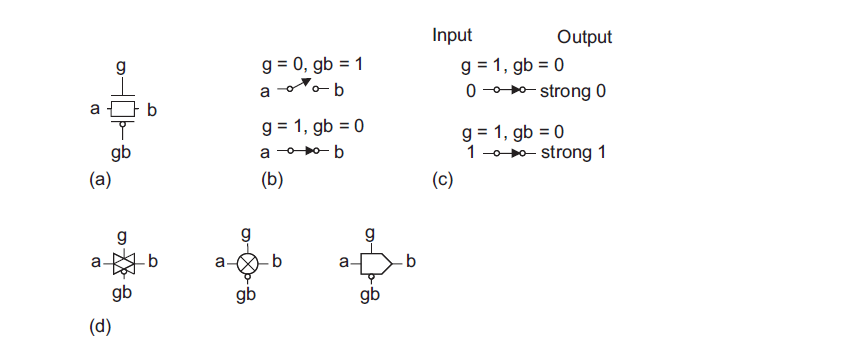

是的!电路如下图(a)所示,当给g高电平,gb(即是g的互补输入相当于~g)低电平的时候这个电路善于同时导通0和1,因为nMOS和pMOS同时导通。 而g和gb就是这个传输门的(互补)控制端,也被叫做双轨(double rail)逻辑。图(d)就是传送门的符号咯,认识就行。

现在回顾之前的NAND和NOR那些线路图。记得上拉网络和下拉网络不--现在一看,上拉网络就是善于传递1,下拉网络就是善于传递0嘛。这样Y才会得到稳定的(strong)输出。顺便提一下,这样的电路被叫做“fully restored”逻辑门(就是即使外界电场变化,输出也很稳定,就像被加了反馈一样)。其实很多复杂的电路是没有办法设计成这么理想的状态,这种情况下就要特殊对待咯。以后会说到。

根据以上这些分析,我提出一个观点:在设计CMOS电路时要避免用非反向逻辑(就是一定要多用反向逻辑)。例如,要多用NOR,NAND,NOT而少用OR,AND,“非NOT”。大家想一想为什么。(提示:从最简单的NOT门,画出其相反逻辑的线路图,综合以上分析,就能得出答案。)

=======================================================以下是答案================================================

画出来非“NOT”的实现,就会发现,要做成CMOS,pMOS要接地,而nMOS接VDD,这岂不是让nMOS导通1,pMOS导通0嘛,所以输出会衰减,就是很不稳定!明白了吧,所以作为一个设计原则,尽量用反向逻辑。以后看谁画的电路图,用了一堆AND/OR那么这个工程师就有可能不太合格~~。那么大家来重新画一下之前提到的AOI22的逻辑实现吧。下面有答案,不许偷看哦(有人说,不是画过了嘛。记住我们要走向大师级,就必须达到一提起来家思索就能画出来的程度,多做几遍有好处)

=======================================================以下是答案================================================

上面两组是复习怎么设计路线图和DeMorgan定律,下面的是线路图与符号。

本文出自 “从基础走向大师” 博客,请务必保留此出处http://physic.blog.51cto.com/1656469/1305229

- 1.3节 逻辑门与二进制数 part4

- 1.3节 逻辑门与二进制数 part1

- 1.3节 逻辑门与二进制数 part2

- 1.3节 逻辑门与二进制数 part3

- 1.3节 逻辑门与二进制数 part5

- 3.二进制数的应用、逻辑学及逻辑门

- 传感器状态与二进制数

- 二进制数与汉诺塔问题

- 十进制数与二进制数的转换

- part4

- 《网络工程师》 Part4 局域网与城域网

- 二进制数、八进制数、十六进制数与…

- 二进制数与十六进制数之间如何互相转换

- 二进制数

- 二进制数

- 逻辑中的二进制

- 继电器与逻辑门

- 32位二进制数与16位二进制数相乘,在屏幕上输出结果

- 1.2节 MOS基本构成 --续

- 1.3节 逻辑门与二进制数 part1

- 1.3节 逻辑门与二进制数 part2

- 1.3节 逻辑门与二进制数 part3

- 开关电源设计入门到精通系列--序

- 1.3节 逻辑门与二进制数 part4

- 1.3节 逻辑门与二进制数 part5

- 1.4三态缓存(tristate buffer)与 多路复用器(Multiplexers)

- 第三章 3.1 精通HDL语言:Verilog,VHDL -序

- 1.5节 卡诺图以及布尔代数(SOP,POS)part1

- 1.5节 卡诺图以及布尔代数(SOP,POS) part2

- 1.5节 卡诺图以及布尔代数(SOP,POS) part3

- 1.1节 Buck Converter--降压转换器 part1

- 1.6节 K图应用:七段译码器