modelsim和debussy的配置

来源:互联网 发布:淘宝买主板 编辑:程序博客网 时间:2024/05/16 09:29

配置篇

; Veriuser = veriuser.sl

Veriuser = novas.dll实战篇

│ rtl.f│ run.bat│ sim.do│ └─rtl clk_rst.v divider.v divider_tb.v

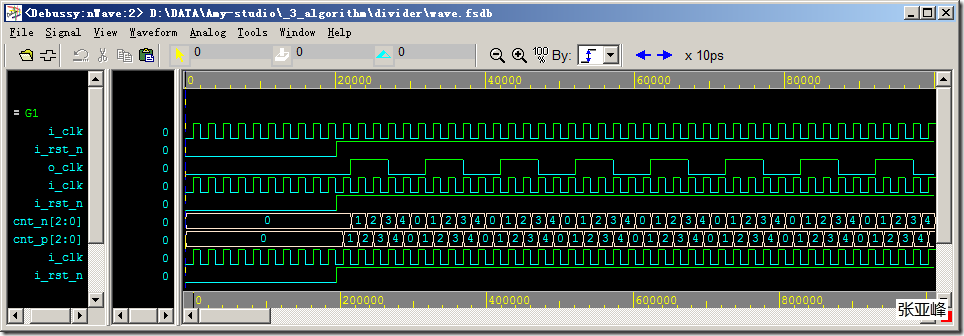

`timescale 1ns/10psmodule divider( input i_clk, input i_rst_n, output o_clk); parameter U_DLY = 1;// log2(5) = 2.3219 <= 3 reg [2:0] cnt_p; // 上升沿计数子 // 5位上升沿计数器: 0 ~ 4// 4 = 5 - 1always @ (posedge i_clk, negedge i_rst_n)begin if (!i_rst_n) cnt_p <= 0; else begin if (cnt_p == 4) cnt_p <= 0; else cnt_p <= #U_DLY cnt_p + 1'b1; endend// log2(5) = 2.3219 <= 3 reg [2:0] cnt_n; // 下降沿计数子// 5位下降沿计数器: 0 ~ 4// 4 = 5 - 1always @ (negedge i_clk, negedge i_rst_n)begin if (!i_rst_n) cnt_n <= 0; else begin if (cnt_n == 4) cnt_n <= 0; else cnt_n <= #U_DLY cnt_n + 1'b1; endend reg o_clk_p; // 上升沿时钟输出寄存器// 输出上升沿时钟// 0 ~ 2 ↑-> 1// (2+1) ~ 4 ↑-> 0// 2 = 5>>1// 4 = 5 - 1always @ (posedge i_clk, negedge i_rst_n)begin if (!i_rst_n) o_clk_p <= 0; else begin if (cnt_p <= 2) // 2 = 5>>1 o_clk_p <= 1; else o_clk_p <= 0; endend reg o_clk_n; // 下降沿时钟输出寄存器// 输出下降沿时钟// 0 ~ 2 ↓-> 1// (2+1) ~ 4 ↓-> 0// 2 = 5>>1// 4 = 5 - 1always @ (negedge i_clk, negedge i_rst_n)begin if (!i_rst_n) o_clk_n <= 0; else begin if (cnt_n <= 2) // 2 = 5>>1 o_clk_n <= 1; else o_clk_n <= 0; endendassign o_clk = o_clk_n & o_clk_p; // 按位与(作用:掩码) endmodule

`timescale 1ns/10psmodule clk_rst( output reg i_clk, output reg i_rst_n);parameter CLK_PERIOD = 20;parameter MULT_RATIO = 10;parameter RESET_TIME = MULT_RATIO * CLK_PERIOD + 1;initialbegin i_rst_n <= 1'b0; #RESET_TIME i_rst_n <= 1'b1;endinitialbegin i_clk <= 1'b0; forever #(CLK_PERIOD / 2) i_clk <= ~i_clk;endendmodule

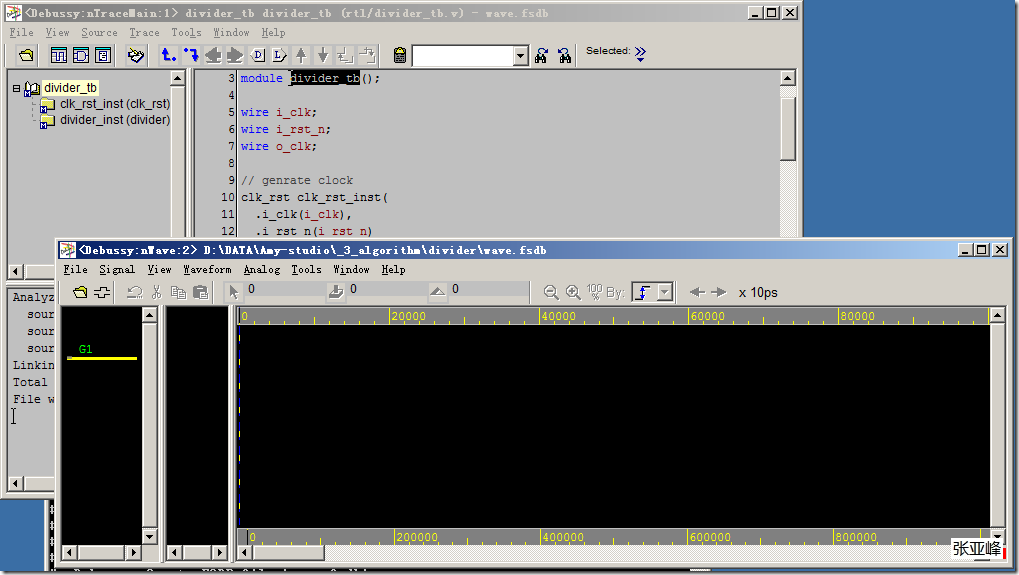

`timescale 1ns/10psmodule divider_tb();wire i_clk;wire i_rst_n;wire o_clk;// genrate clockclk_rst clk_rst_inst( .i_clk(i_clk), .i_rst_n(i_rst_n));// user logicdivider divider_inst( .i_clk(i_clk), .i_rst_n(i_rst_n), .o_clk(o_clk));// dump fsdb file for debussyinitialbegin $fsdbDumpfile("wave.fsdb"); $fsdbDumpvars;endendmodule// dump fsdb file for debussyinitialbegin $fsdbDumpfile("wave.fsdb"); $fsdbDumpvars;endrtl/divider.vrtl/clk_rst.vrtl/divider_tb.v

vlib workvlog -f rtl.fvsim work.divider_tbrun 10usq

::关闭回显@ECHO OFF::设置软件路径SET debussy=C:\Novas\Debussy\bin\Debussy.exeSET vsim=C:\modeltech_6.5\win32\vsim.exe::ModelSim Command%vsim% -c -do sim.do::删除ModelSim生成的相关文件RD work /s /qDEL transcript vsim.wlf /q::Debussy Command%debussy% -f rtl.f -ssf wave.fsdb -2001::删除波形文件DEL wave.fsdb /q::删除Debussy生成的相关文件RD Debussy.exeLog /s /qDEL debussy.rc /q::退出命令行EXIT

- modelsim和debussy的配置

- 【modelsim和debussy】设置

- Modelsim+Debussy联合使用

- ModelSim 与Debussy联调

- modelsim与debussy联调环境的搭建

- modelsim与debussy联调环境的搭建

- Debussy

- Debussy

- modelsim批处理和xilinx core的使用

- ISE与modelsim的安装和使用

- Quartus II和Modelsim的联合仿真

- Modelsim do文件和批处理文件的使用

- debussy分块dump波形的命令

- verdi/debussy的快捷键 以及基本操作

- verdi/debussy的快捷键 以及基本操作

- ISE与Modelsim联合仿真配置和技巧

- ModelSim手动配置方法

- modelsim 仿真配置

- war文件

- 一个非常好的OpenGL外文博客

- MySQL数据库设置远程访问权限方法小结

- JMeter: java.net.BindException: Address already in use: connect

- matlab 笔记

- modelsim和debussy的配置

- 通向架构师的道路(第十九天)使用maven构建Spring工程

- 查询通讯录-1(数据库结构)

- Oracle用户和模式的区别

- 提交表单的时候,后台走了两遍

- 通向架构师的道路(第二十天)万能框架spring(二)maven结合spring与ibatis

- 编辑框根据显示数据自动垂直滚动到底端的方法

- 通向架构师的道路(第二十一天)万能框架spring(三)之SSH

- 【解决方法】Could not find the main class Program will exit