D触发器二分频电路

来源:互联网 发布:windows mail在哪 编辑:程序博客网 时间:2024/04/30 06:17

D触发器二分频电路

有时真的要感慨一下自己电路学的够烂的,啥都不会,做示波器要学习分频电路,学呗。。

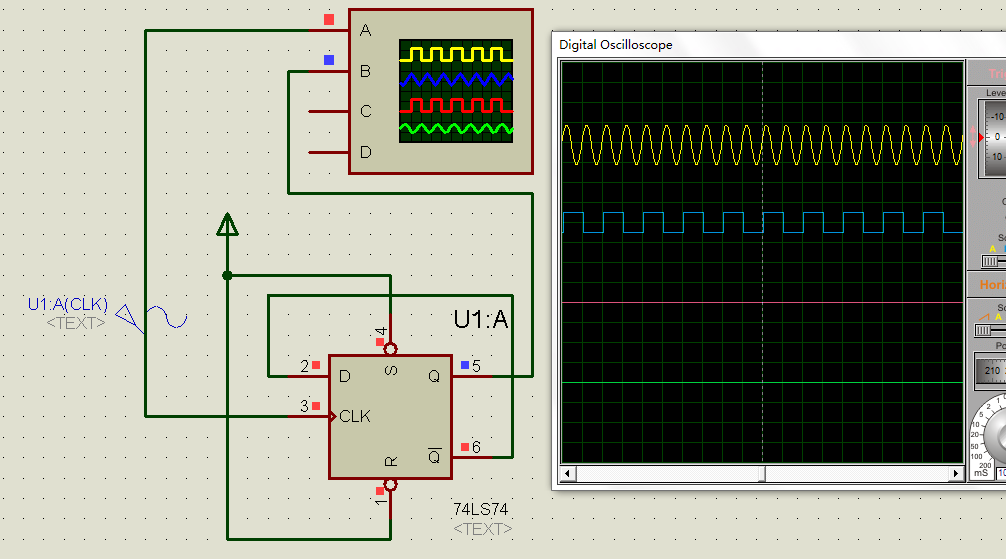

将D触发器的Q非端接到数据输入端D即可实现二分频,说白了就是CLK时钟信号的一个周期Q端电平反转一次,很好理解。

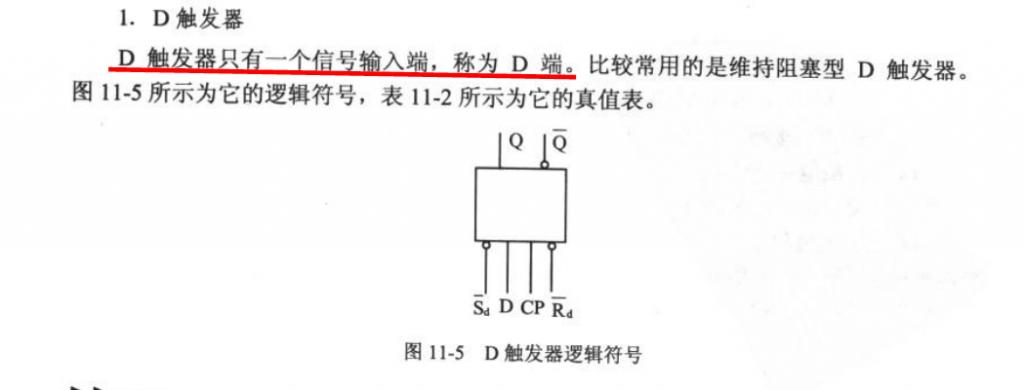

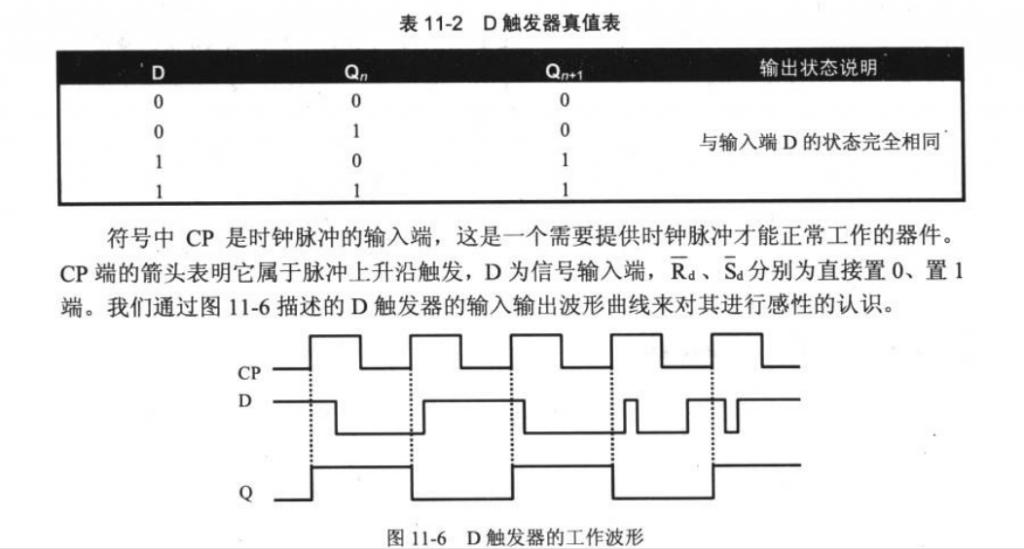

S 和R 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。当S=1且R=0时,不论输入端D为何种状态,都会使Q=0,Q非=1,即触发器置0;当S=0且R=1时,Q=1,Q非=0,触发器置1,S和R通常又称为直接置1和置0端。我们设它们均已加入了高电平,不影响电路的工作。

今天也简单看看74系列芯片,也总结一下:

1.74ls为TTL电平,74hc为CMOS电平

2.TTL不能直接驱动CMOS电平,需要加上拉电阻,而CMOS可以直接驱动TTL

3.TTL器件需5V供电才能工作,CMOS则为2-6V

4.74系列为民用,54系列为军工产品

分类: 电子电路

0 0

- D触发器二分频电路

- D触发器的二分频电路

- 分频电路

- 分频电路(偶分频、奇分频)

- 一个比较简单的D触发器4分频verilog程序

- 分频电路(转)

- 分频电路(转)

- [matlab]余弦分频电路

- 分频电路-verilog

- 用Verilog实现电路分频

- Verilog任意整数分频电路

- 欧姆龙PLC分频电路

- 从计数器到分频电路

- 用Verilog语言实现奇数倍分频电路3分频、5分频、7分频

- 利用触发器生成三分频

- 关于3分频电路的讨论

- 触发器及其电路分析

- 使用D触发器制作正交编码器的鉴相电路(转)

- 剑指offer面试题 替换空格

- easyui datetimebox 如何只显示 月份,不显示具体的数据

- modbus 协议(1)

- view事件传递

- ubuntu16.04使用手札(二)——分区管理

- D触发器二分频电路

- 求二进制中1的个数----Java实现

- MFC中Spin control的使用

- 剑指offer(二十一)之和为S的两个数字

- Android Log统一管理类

- MIPI2---- DBI\DPI\DSI简介

- figure元素

- 多线程异常 和 事务(一)

- Android JNI: Can't include C++ headers like vector or string...