Verilog学习笔记5:层次化设计-数码管段选

来源:互联网 发布:天津平面设计美工培训 编辑:程序博客网 时间:2024/04/30 08:13

从这篇日志开始,将以一个实例(数码管的应用),用多个篇幅来介绍Verilog的层次化设计方法。

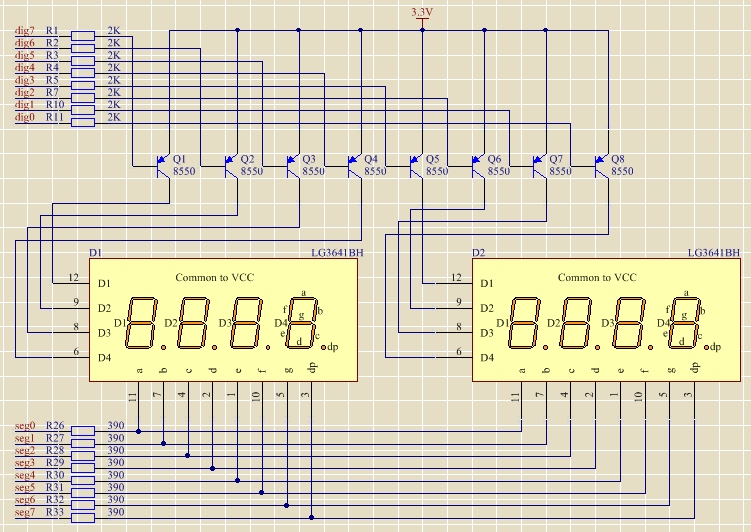

本日志介绍数码管段选电路的设计,先看电路图。

段选用于在数码管上显示数字(0-9)、字母或其它字符,本例仅以显示字符为例,让数码管的每位显示相应的数字(0-9)。

由于0-9只有10个数字,所以我们用4位二进制,便可以表示,Verilog代码如下:

CSDN:http://blog.csdn.net/qingwufeiyang12346。

本日志介绍数码管段选电路的设计,先看电路图。

段选用于在数码管上显示数字(0-9)、字母或其它字符,本例仅以显示字符为例,让数码管的每位显示相应的数字(0-9)。

由于0-9只有10个数字,所以我们用4位二进制,便可以表示,Verilog代码如下:

module mod_seg (number, seg);

input[3:0] number;

output[7:0] seg;

reg[7:0] seg;

parameter SEG0 = 8'b11000000;

parameter SEG1 = 8'b11111001;

parameter SEG2 = 8'b10100100;

parameter SEG3 = 8'b10110000;

parameter SEG4 = 8'b10011001;

parameter SEG5 = 8'b10010010;

parameter SEG6 = 8'b10000010;

parameter SEG7 = 8'b11111000;

parameter SEG8 = 8'b10000000;

parameter SEG9 = 8'b10010000;

parameter SEGN = 8'b11111111;

always @(number)

begin

case(number)

4'd0:seg <= SEG0;

4'd1:seg <= SEG1;

4'd2:seg <= SEG2;

4'd3:seg <= SEG3;

4'd4:seg <= SEG4;

4'd5:seg <= SEG5;

4'd6:seg <= SEG6;

4'd7:seg <= SEG7;

4'd8:seg <= SEG8;

4'd9:seg <= SEG9;

default: seg <= SEGN;

endcase

end

endmodule

解释如下:

1、代码首先定义模块,并命名为mod_seg,意为段选模块。

2、模块带有2个端口,第1个端口为number用于表示输入的数字,第2个端口seg为端码,用于在数码管上显示相应的数字。

3、定义端口number的方向为输入(4位),定义端口seg的方向为输出(8位)。

解释如下:

1、代码首先定义模块,并命名为mod_seg,意为段选模块。

2、模块带有2个端口,第1个端口为number用于表示输入的数字,第2个端口seg为端码,用于在数码管上显示相应的数字。

3、定义端口number的方向为输入(4位),定义端口seg的方向为输出(8位)。

4、定义seg为寄存器型,以便于在always@中同时动作,以避免“竞争-冒险”现象的发生。

5、定义端码参数,以增强代码的可读性。

6、在always@中完成数字到段码的转换。

6、在always@中完成数字到段码的转换。

有任何问题欢迎留言,我尽最大可能予以解答,知而获智,智达高远。

原创性文章,转载请注明出处 http://user.qzone.qq.com/2756567163。 CSDN:http://blog.csdn.net/qingwufeiyang12346。

阅读全文

1 0

- Verilog学习笔记5:层次化设计-数码管段选

- Verilog学习笔记6:层次化设计-数码管位选

- 数码管段选码表,你值得get

- Verilog的层次化设计

- 单片机数码管段码

- 单片机数码管段码

- verilog 层次化设计语言调用的问题终于知道了

- FPGA学习(第10节)-模块的例化-Verilog层次化设计实现LED流水灯

- 八段LED数码管段代码编码表

- 每天一点Verilog,《高级FPGA设计》学习笔记:综合编码

- 【学习笔记】【第一章】【Verilog HDL数字集成电路设计方法概述】

- Verilog学习笔记

- Verilog初步学习笔记

- Verilog 学习笔记

- Verilog学习笔记一

- verilog状态机学习笔记

- Verilog学习笔记

- VGA学习笔记(verilog)

- Apache服务的基础

- 20170517

- 关于js中的delete操作符

- caffe的CMakeList.txt注释

- 数据结构和算法的选择

- Verilog学习笔记5:层次化设计-数码管段选

- 消息队列的实现

- mysql

- 虚幻4C++编程入门(搬运1)

- 在eclipse查看HttpServlet源码

- java 重写、重载以及多态

- go map slice积累

- 由于目标计算机积极拒绝,无法连接--mongoDB连接错误;以Windows Service的方式启动MongoDB

- Yocto 环境搭建